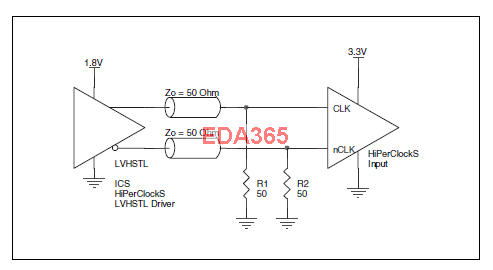

不同的差分电平怎么相接?

像上面这个图,接收器的参数如下:

symbol Parameter Min typical Max Units

------------------+-----------------------------------------+--------------+---------------+---------------+-------------

Vcc Core Supply Voltage 3.135 3.3 3.465 V

Vih Input High Voltage 2 Vcc+0.3 V

Vil Input Low Voltage -0.3 0.8 V

Vpp Peak-to-Peak Input Voltage 0.15 0.3 V

------------------+-----------------------------------------+--------------+---------------+---------------+-------------

我不明白为什么参数里写着Vih.Min为2V,怎么还可以接收1.8V的LVHSTL电平?

那如果可以接收1.8V的LVHSTL电平,那能不能接收1.5V的SSTL电平呢?

不同的差分电平只是偏置电压不同、上下摆幅不同吗?

我也很想知道,求高手解答

我以前都没碰到过 LVHSTL 电平 能简单描述一下吗?

能不能把发送器的参数贴上

回复 cwfang 的帖子

谢谢关注!

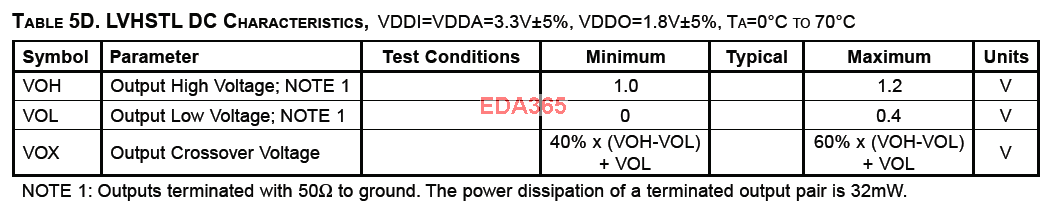

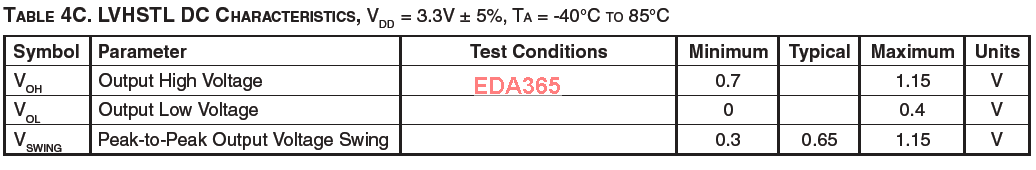

我找到两个LVHSTL驱动器的参数,不太相同,如下

可以看出输出电压都低于2V,为啥接收器还能接收?

那它能接受1.5V SSTL差分电平吗?(也有地方称作1.5V CMOS电平),我自己对这个电平也有点糊涂了。

回复 cwfang 的帖子

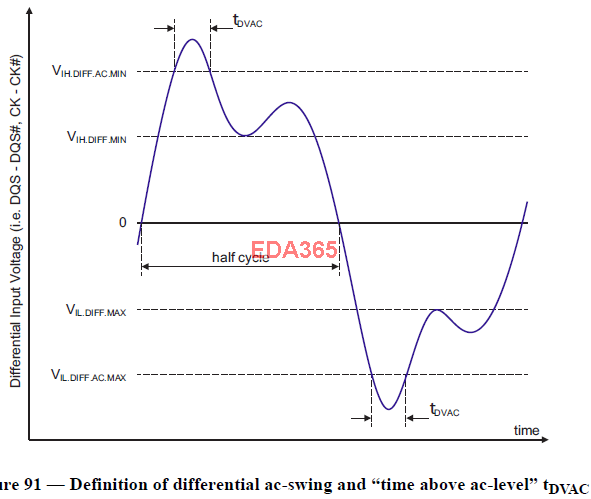

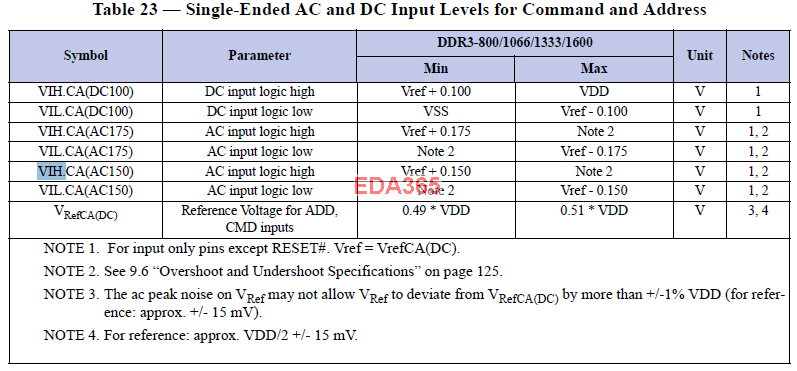

关于1.5V SSTL差分电平我只能提供下面这些数据,这个电平是内存时钟信号的电平,我自己也不太理解。

差分电平的一些参数:

其中一些要用到单端电平的参数,如下,VDD为1.5V,Vref为0.75V

我的任务就是找到一个这样的芯片:

它能接受1.5V SSTL电平的400MHz差分时钟,将之倍频,输出最好还是1.5V SSTL电平。

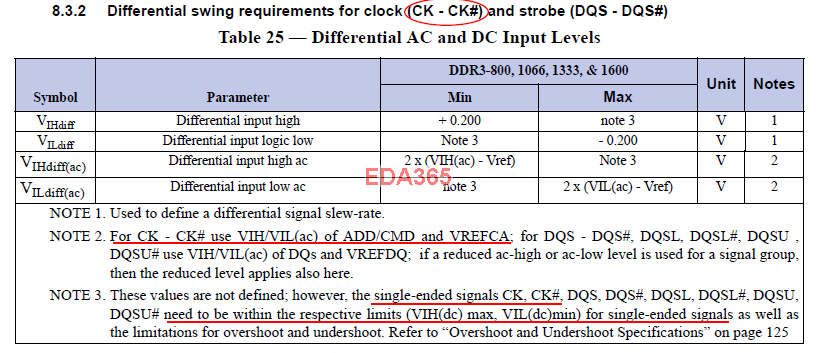

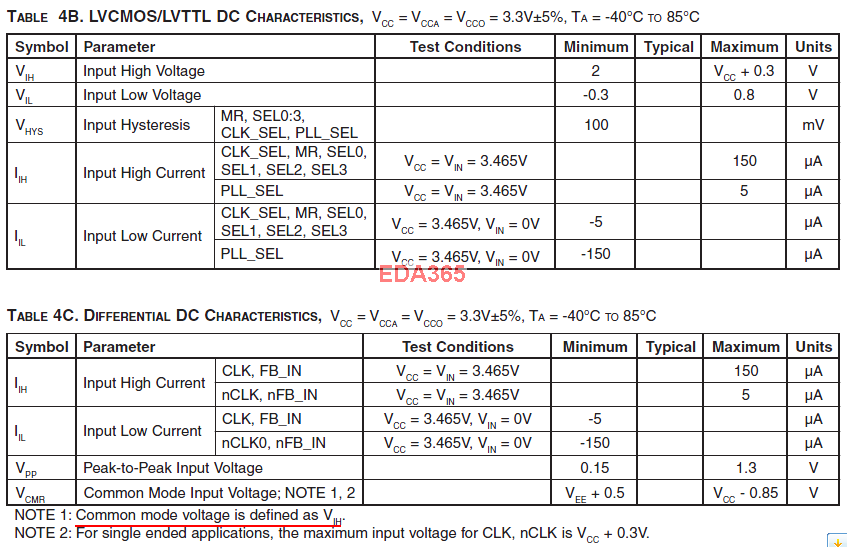

现在找到一个芯片ICS873S02I ,可以接受SSTL电平,但是我不确定能不能接受1.5V SSTL,因为SSTL还有1.8V、2.5V、3.3V,datasheet里也没说清楚,刚又重新看了一遍datasheet,发现1楼里我截取出来的信息理解有误,这里把原始信息贴上。

Vih,Vil是指的芯片的其他控制信号,并不是输入的时钟信号,但是画红线的部分又让我迷惑了。

从你贴的图中可以看到 发送端的VOH最大为1.2V,对于接收端来说,1.2是个不定状态,所以个人感觉应该是不对的。两种电平方式想要直接连接,必须满足两个条件:1、发送方VOH大于接收方VIH,提供一定的噪声容量,2、发送方的VOL小于接收方的VIH,并且提供一定的噪声容量

回复 cwfang 的帖子

参数里好像并没有给差分接收端的Vih和Vil,只给了个Vpp。

不知道差分电平的接收和单端电平的接收有何不同?

还有common mode 是什么意识?

你图上不是已经贴出来了吗?接收端的VIH=2,VIL=0.8,看这个是不满足要求的,common mode 是共模信号,差分分为差模和共模,共模是噪声,差模是有用的信号

回复 cwfang 的帖子

这个主要是我一开始理解有误,后来也没说清楚。

Vih和Vil是芯片的其他一些单端控制信号的参数,并不是差分信号的参数。对于差分信号,只提供了Iih、Iil和Vpp,见8楼table 4C。

我现在想知道对于差分信号的接收端来说,是不是只关心Vpp,而不关心单根信号的Vih、Vil?

使用相应的电平转换芯片即可,不要忘了电阻匹配网络。

回复 fanxingfast 的帖子

SSTL15电平比较特殊,没有专门的转换芯片,除了最高电平为1.5V外,我也不知道它特殊在哪,所以想问有没有什么方法可以让A差分电平的接收器接收B差分电平的信号?

比如通过在接收端加上下拉电阻,设置偏压,因为我现在对不同差分电平的理解就是偏置不同,摆幅不同。

差分信号主要看摆幅是否兼容,接收器的输出摆幅最大是0.3V,发送器的摆幅最小为0.3V,显然是满足要求,发送端的摆幅大于接收端的,其实差分信号还有偏置电压的问题,不过这里你好像没有提到。如果偏置电平不一样,还需要转换一下