请高手帮忙看看晶振的分压和布线是否合理

时间:10-02

整理:3721RD

点击:

我们现在的情况:

1 为了降低功耗,我们用一个有源27M晶振同时给DSP和FPGA提供时钟,这样可以减少一个晶振。

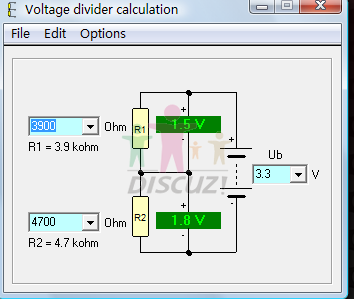

2 因为DSP和FPGA需要的电平为1.8V,所以把晶振的输出波形做了分压处理,如图所式。

问题1:

用电阻分压的方法使晶振的输出波形由3.3v转换到1.8v的办法是否合理,有没有问题?

问题2

用一个晶振同时给DSP和FPGA提供时钟的方法必然导致时钟线的延长,但是考虑到是有源晶振,不是两个脚的晶体,时钟线延长是否没有什么问题?时钟线的布线如图所示,时钟线从晶振到DSP的距离是27mm,到FPGA的距离是36mm

加亮的线是时钟的实际走线

求助高手!

这个,感觉有点悬哎,最好做一个基本的信号完整性仿真

我用99se画的,仿真不好做,而且没有做过,请高手指教

我初步仿真了一下,时钟的沿还是不太好。如果一定要这样用,我建议一下几个措施:

1.如果fpga的端口可以配置成施密特触发的输入结构,使用它,以下基于这点。如果cpu的时钟也是施密特触发(一般时钟端口都是),就很好。这时基本上可以冒险试试。

2.如果的fpga有剩余的端口,建议时钟只进入fpga,然后fpga做一个缓冲,再给cpu。以下建议基于这点。

3.分压电阻放在靠近fpga的一段好些,这时沿可以陡一些(我只做了时钟输入到一个芯片的仿真)。

4.如果fpga有多余的pll,可以把晶振的时钟降低,然后用fpga的pll倍频到cpu所需要的时钟,再送给cpu。这样会好很多,多功耗也好。

一下子只想到了这些,如有不对的地方,欢迎大家指正。

另外,你的3.3V到1.8V转换的电阻好像用的不对。分压值不对。

建议分得的适当电压小一些,防止过冲对芯片的损害。

请问用什么软件可以仿真这种电子图!?

才27M 不会有什么问題

如果输出的时钟信号先 能够很好的被保护起来的话可能问题不是很大,不过从现在的走线来看,附近情况有些不太理想。我想主要需要解决的问题是防止附近的数字信号干扰时钟信号,使接收到的时钟信号不产生畸变。