s3c6410 PCB工艺和叠层请教讨论

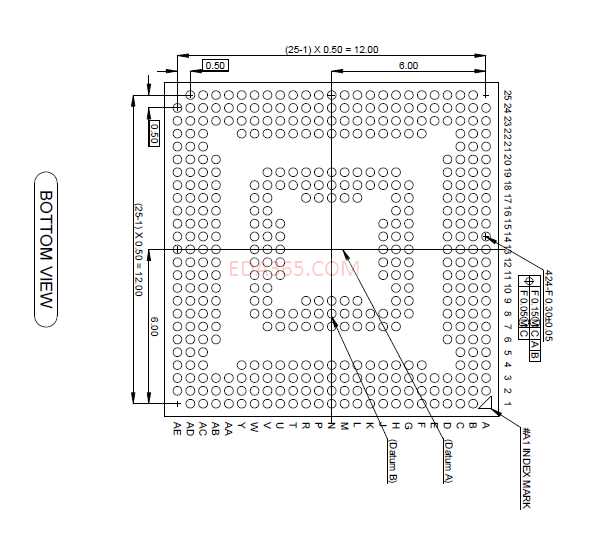

三星的s3c6410的封装是0.5mm的BGA,希望做过这个片子的同仁和感兴趣的PCB高手能讨论一下做这个片子的的最小工艺要求。我初步设想需要8层板,0.08mm的线宽/线间距。0.15mm/0.25mm的过孔,SGSGPSGS叠层。盲孔工艺。不知道是否合适?或者有其它的方案,原则是可以做,稳定可靠,基本对板子大小没有要求。希望大家多多指教。附图是封装图。

之前我做过一块6410的板子,用的也是八层板:GSGSGPSG,0.1mm的线宽/线间距,盲孔埋孔都用到。板子很稳定!

谢谢figofeng,0.5mm的BGA的焊盘是0.25mm,两个焊盘之间只有0.25mm的距离。

不知道你的过孔和盲埋孔是多大规格,0.1mm的线宽/线间距怎么扇出啊,谢谢。

能不能说一下你的具体的盲埋孔的设计,孔径大小和叠层,谢谢!

你告诉我QQ吧!

层叠:g-s-g-s-v-g-s-g

1-2、7-8层盲孔外径10mail,内径4mail

2-7层埋孔外径18mail,内径10mail

线宽线距:4mil

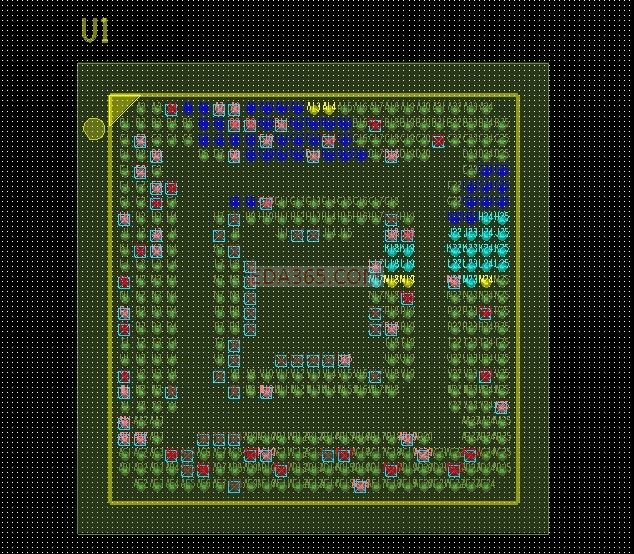

BGA内尽量靠近焊盘打盲孔,甚至可以重叠一部分。使用盲孔将线导入到内层,然后再直接走线,或者通过埋孔将走线引到其它的层进行走线!

看BGA的出线多不多,建议尽量在top和L2走线,在内层要打一个2-7层埋孔,占很多地方

层叠:s-s-g-s-v-g-s-g

1-2、7-8层盲孔外径10mail,内径4mail

2-7层埋孔外径18mail,内径

top层为了在2个焊盘中间走一根线,焊盘是0.25mm,线宽0.1,线距0.075mm

其它层线宽线距4mil

感谢大家的支持。

如果我这样做,不知道成本会差多少?

孔:1-2,3-4,5-6,7-8,1-4,5-8,1-8,外径:0.25mm,内径:0.1mm(4mil)

最小线宽/线距:0.08mm。

------------------------------------------------------------------------------------------------

1-2、7-8层盲孔外径10mail,内径4mail

2-7层埋孔外径18mail,内径10mail

线宽线距:4mil

这个芯片需要那么多类型的孔么?你那么多类型的孔,价格回很贵的

这样,看来做

1-4,5-8的盲孔,外径:0.25mm,内径:0.1mm(4mil),

1-8的通孔,外径:0.3mm,内径:0.15mm,

这样的方案是不是性价比好些,比起做HDI工艺来说?

figofeng 你qq多少呢?

大家好!我做了一块s3c6410的PCB,六层板,层叠:S-P-S-S-G-S,过孔都为通孔:外径0.25mm ,内径为 0.15mm,但线与过孔的间距不到3mil,加工起来有困难,请问大家6410必须用盲,埋孔吗,谢谢

我的线宽/线距均为 4mil,希望能交流,我的QQ:23427341

楼上的,如果你把线宽/线距改为3mil/3mil可能会好些。我现在做的是线宽/线距为0.8mm/0.8mm。

你全部用通孔CPU是怎么扇出的,高手啊,还望指教一下。

层叠:S-P-S-S-G-S,BGA内部间距0.08mm,全局0.1mm,via-pad(0.1mm/0.2mm激光孔)。全局过孔0.2/0.4mm.

谢谢楼上,至于扇出可以用手工一个个打出来或在ROUTER里面扇出,按照左下、右上;

楼上的BGA内部间距0.08mm,全局0.1mm,via-pad(0.1mm/0.2mm激光孔)。全局过孔0.2/0.4mm,能加工吗,是到哪加工的,方便发个邮件 zhx224@yahoo.com.cn ,感谢!