为何异步复位那要加2个D触发器才能保证无亚稳态?

时间:10-02

整理:3721RD

点击:

为何异步复位那要加2个D触发器才能保证无亚稳态?

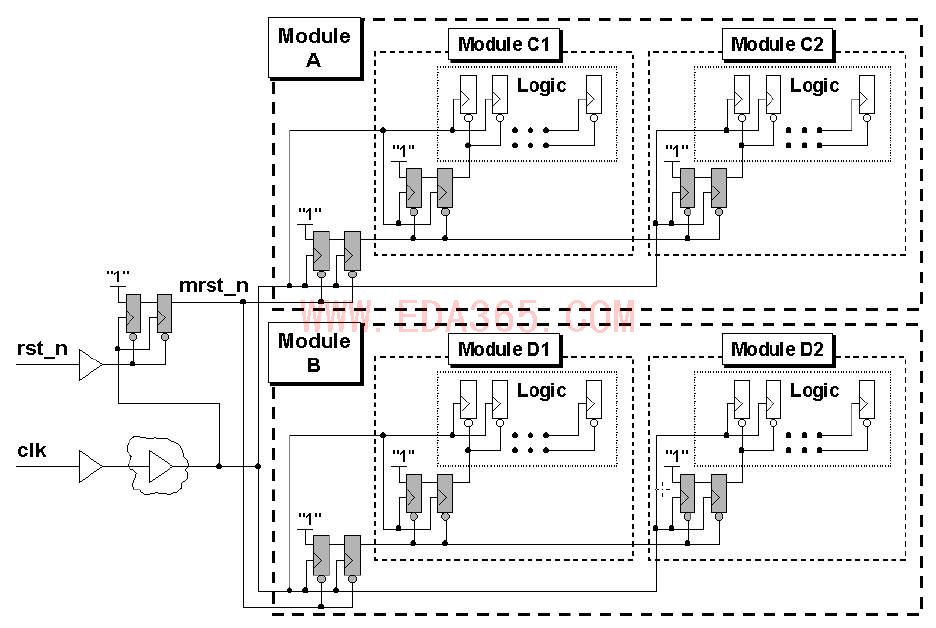

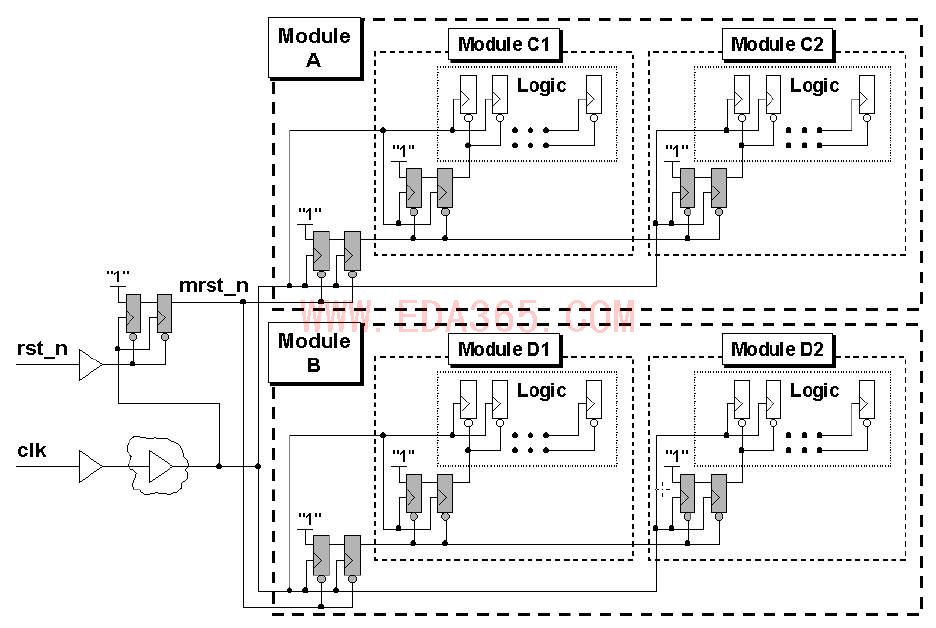

其中P是一个触发器发生亚稳态错误的概率。标准的方法是采用至少两个触发器(有时采用3个)

进行同步串联。

3:使用能克服亚稳态的触发器。这些器件内部的触发器电压低且速度快,具有很大的K值,

输出驱动同普通触发器是一样的,具有很好的亚稳态性能。

4:尽量降低采样频率(如果可能)。较宽的时钟周期使得触发器有充分的时间进行反应,

使得采样到亚稳态的机率减少。如果时钟频率降低,失效率会比指数速率下降得还要快。

5:如果输入信号的变化很慢,一些触发器的亚稳态性能会变差。采用边沿速度快的输入信号可以克服这个问题

适当延时,给复位稳定的触发信号!

(转摘)

如果遇到亚稳态问题,下面的建议可能会有帮助:

1:采样快速触发器,这种触发器可能有较窄的亚稳态时间窗。

2:将两个(或多个)触发器串联,用同一个时钟驱动。N个触发器发生错误的概率是

其中P是一个触发器发生亚稳态错误的概率。标准的方法是采用至少两个触发器(有时采用3个)

进行同步串联。

3:使用能克服亚稳态的触发器。这些器件内部的触发器电压低且速度快,具有很大的K值,

输出驱动同普通触发器是一样的,具有很好的亚稳态性能。

4:尽量降低采样频率(如果可能)。较宽的时钟周期使得触发器有充分的时间进行反应,

使得采样到亚稳态的机率减少。如果时钟频率降低,失效率会比指数速率下降得还要快。

5:如果输入信号的变化很慢,一些触发器的亚稳态性能会变差。采用边沿速度快的输入信号可以克服这个问题

很好 很强大

解释得比较清楚,不错

很清晰的问题和解释,学习了

en 说不不错

呵呵 不错学习!