新手关于PADS的几个问题 希望朋友们指导

2:四层版 四层敷铜属性可不可以都设置成地?

3:每个元件间的地引脚可不可以不用走线,直接敷铜当作走线?

4:封装丝印一般有什么要求

5:原理图上有很多R阻值为0还有很多电阻标记为NC,是什么意思,有什么作用?

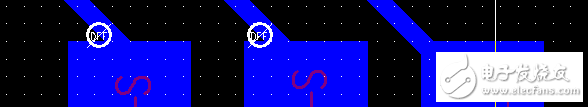

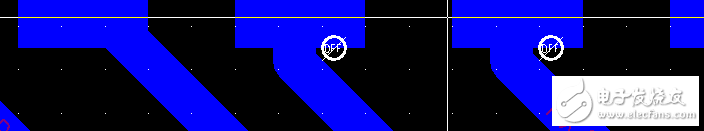

6:引脚的出线方式,如截图,为什么会有那么多提醒,该怎么出线比较好?

纯新手,没有经验,第一次layout,也没有PCB生产制作经验,望大神朋友们指点,谢谢

XN8(D6O%)X07{$`8ZW`5T`0.png(6.17 KB, 下载次数: 0)

下载附件 保存到相册

2016-7-8 14:04 上传

1:PCB板子上有大量的过地孔,是人为一个一个加上去的么?

可以一次性放多个过孔,批量修改属性.

2:四层版 四层敷铜属性可不可以都设置成地?

这个看具体情况,看你不同覆铜层的功能需求,模拟电路的话,可以都覆铜地.

3:每个元件间的地引脚可不可以不用走线,直接敷铜当作走线?

可以,但是覆铜当走线有一定风险,可能导致漏走,或者有些覆铜接触很勉强.

4:封装丝印一般有什么要求

要求按照厂家的生产工艺定,字符清晰整齐就可以了.

5:原理图上有很多R阻值为0还有很多电阻标记为NC,是什么意思,有什么作用?

0欧电阻用处很多,你可以百度一下,NC就是 noconect,不用焊接.

6:引脚的出线方式,如截图,为什么会有那么多提醒,该怎么出线比较好?

一看那就不是什么正经走线,中心引出以后,你再拐弯就好.

我也刚学习pads,以后可以切磋一下。关于你的问题,只捡两个懂点的回答,第一个是人为放上去的。不可以都设置成GND.像0欧电阻和NC大多时候是预留出来的位置,方便以后更改。

全部设置成GND 不是可以更好的屏蔽 更好的提供回流路径么

第六个 我已经知道了 是酸角问题(锐角问题),在信号方面这样走线会加重电磁干扰(别人说的),在生产方面锐角处不容易敷铜(走线容易断路)

你知道这是什么原因么?谢谢喽!

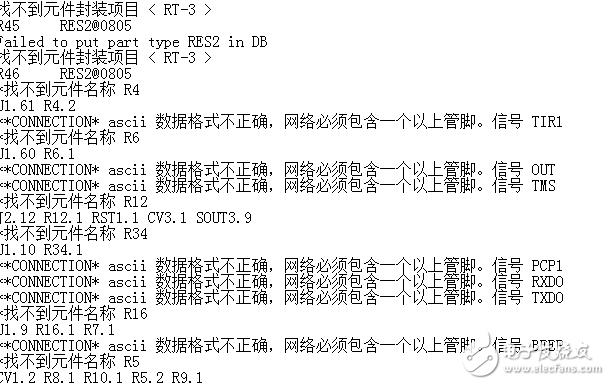

我今天导出的PCB库,可是出现老多报告错误。如上图。正在查找原因呢。

参考的:一般来说都是在电源输入部分加各种EMI滤波,所以参考地都是选择在整流滤波最近的地。越到后级,由于各级功率拓扑的影响,地线会越来越脏,所以大面积覆铜最好在用在参考地。但是也不是越多越好,普遍认为对于全由数字器件组成的电路应该大面积铺地,而对于模拟电路,铺铜所形成的地线环路反而会引起电磁耦合干扰得不偿失(高频电路例外)。因此,并不是是个电路都要普铜的(BTW:网状铺铜比整块整块的铺性能要好)电路铺铜的意义在于:1、铺铜和地线相连,这样可以减小回路面积2、大面积的铺铜相当于降低了地线的电阻,减小了压降从这两点上来说,不管是数字地,或模拟地都应该铺铜以增加抗干扰的能力,而且在高频的时候还应该把数字地和模拟地分开来铺铜,然后用单点相连,该单点可以用导线在一个磁环上绕几圈,然后相连

原因知道,可以设置焊盘出线方式 就不会出现这种问题了.

PART封装没有匹配

你的pads里面的封装库多么?都是自己建立的么?要是多的话,可以发给我一份么?

不多 都是自己画的

没有包含PCB库