关于三极管的稳压电路的一点疑问

时间:10-02

整理:3721RD

点击:

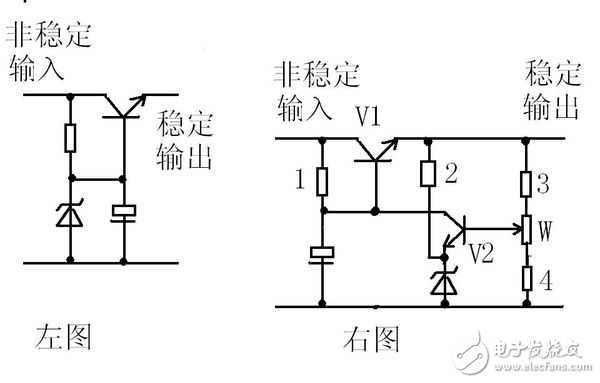

如上图这个稳压电压,说它能稳压,是建立在三极管的be结的压降基本在0.7v左右。但是如果考虑微电流,则情况又是怎样的?

如果负载很小,假设是一块芯片,睡眠时只需要4ua左右的电流,那么PN结在这么小的电流下的压降是很小的,我实测过,200mv不到,而且根据PN结的公式也能得到很小的电压值。此时这个电路的输出电压不就比大电流时的输出电压大了吗?(毫安级别的输出电流,三极管的be结压降是能达到0.6v)

这个问题是基于我实际遇到的,VS1003B芯片的CVDD电压范围2.4~2.8,典型值2.5V,我只有3.3v带使能的ldo,没有2.5v的ldo。VS1003B睡眠模式下电流典型值是3.7uA,工作时电流17.5mA。所以在睡眠模式下,就会出现我上面提到的那个问题。希望高手出来帮我解惑,谢了!

左图确实存在你说的现象,为了避免微电流输出时电压的偏高,可以并联一个预定负载电阻,吸收1ma左右电流,就可以了。右图不存在你说的问题,它的取样电阻就可以吸收大于1ma的电流,从而使结压降保持在0.6v左右。

非常感谢您的回答,我主要考虑左图,你的那个方法我有想过,不过因为系统采用电池供电,所以对功耗的要求有点高,1mA的损耗有点大了

如果负载很小,假设是一块芯片,睡眠时只需要4ua左右的电流,那么PN结在这么小的电流下的压降是很小的,我实测过,200mv不到,而且根据PN结的公式也能得到很小的电压值。此时这个电路的输出电压不就比大电流时的输出电压大了吗?(毫安级别的输出电流,三极管的be结压降是能达到0.6v)

这个问题是基于我实际遇到的,VS1003B芯片的CVDD电压范围2.4~2.8,典型值2.5V,我只有3.3v带使能的ldo,没有2.5v的ldo。VS1003B睡眠模式下电流典型值是3.7uA,工作时电流17.5mA。所以在睡眠模式下,就会出现我上面提到的那个问题。希望高手出来帮我解惑,谢了!

目前的稳压器件的功能,都是建立在器件的工作状态下的。不要说调整三极管,就是那个稳压二极管也需要毫安级的电流来建立工作点。这在稳压管的特性曲线图上就能够看到。如果纠结这几个毫安,那整个稳压状态就根本无法建立,又何谈电压高低。

左图,稳压管是在电阻持续供流下永久导通的,没有负载,射极电压不会升高,

右图,取样(反馈)电阻已是宣泄渠道,因为,流过电阻3的电流必须至少等于V2的基极电流,没负载时,电阻3和4可充当最小负荷。

路过、、、路过、、、、