关于mos隔离后上升沿问题

时间:10-02

整理:3721RD

点击:

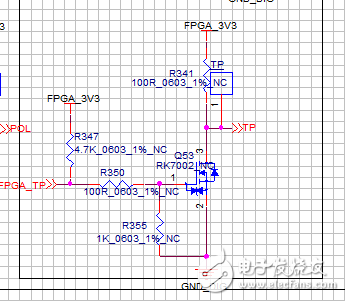

我在设计电路时,从fpga出来的方波波形是很好的,上升沿也是垂直上升的,但经过mos隔离后,上升沿时间变长不在垂直上升。现在想办法需要减少上升沿时间,我的解决方法是将d级上的上拉电阻减小,但在这里想问大家有没有更好的方法

电路

您好,学习一下,资料很好,谢谢了,我是初学者,想多学点知识。

说的不一定对 仅供参考 可以试试

1 R350 100R电阻减小 看下波形

2 R350上 并联一个二级管看下波形

但是R350 过大有损耗 过小 EMC影响所有建议你看下MOS管得资料看看吧 网上我看有利用二极管和三极管来提升上升沿速度的 你找找

驱动电流不足。可以把MOS管换成NPN的试试。不然就要加多个NPN管做E输出的电流放大。

我有试过R350减小,但发现它对下降沿有影响,对上升沿影响不大

我有试过R350减小,但发现它对下降沿有影响,对上升沿影响不大

R350前 后波形一样么?MOS的开关时间多少,你的方波周期多少

我觉得应该减小R355,缩短G极放放电时间

再减小R350没有效果的情况下,可以考虑加个图腾柱增加驱动能力

R355加上,但是要比R350大许多,7倍以上的关系!

学习

可以在E350并联一个小电容