运放输出所接电容和电阻大小的确定?

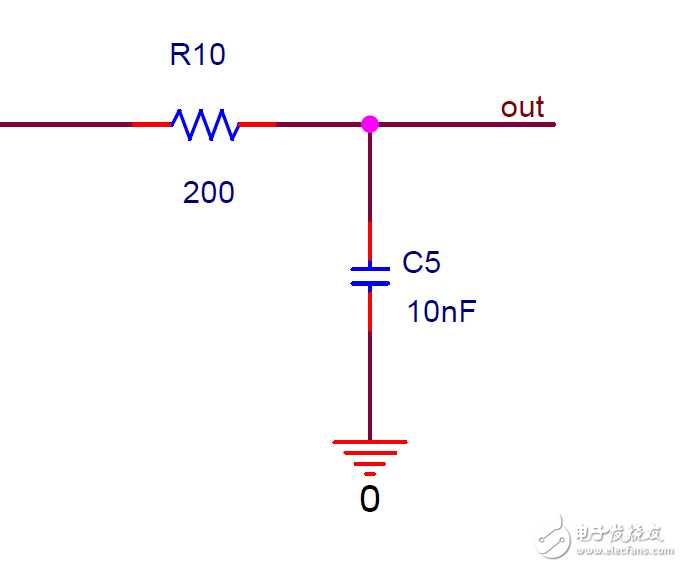

运放输出的是100Hz,12mv的方波,直流,可是会有过冲现象,通过接如图的电路来消除。

问题:

1、电阻和电容的大小选择不合适会形成积分电路,所以怎么权衡电阻和电容的值来保证消除过冲,又不会导致积分的发生?只能通过仿真么?

2、大概做了仿真,得到如图所示的电阻和电容的大小,电容容值太小,nF级别的,实际电路中,可能寄生电容都不止这么多。

但是如果提高了电容值,那电阻值也会相应地提高,输出阻抗太大,会导下一级的电路驱动会受到影响。怎么权衡这个矛盾?

谢谢!

1.减小电容值(没仿真,建议使用图示仿真结果容值,观后效)2.运放输出端不敷地用以减少寄生电容(其实寄生电容达不到NF级别)。

下一级电路可以用射随!

其实这个电路的参数是有公式计算的

1、电阻和电容的大小选择不合适会形成积分电路,所以怎么权衡电阻和电容的值来保证消除过冲,又不会导致积分的发生?只能通过仿真么?

-----滤波电路而已,不要理解到积分电路那么复杂,滤波过度会造成波形边缘特性变差(上升时间、下降时间增加),要预先估计好自己要滤除频率,或者要把冲击抑制到什么程度,仿真是一条很好的路子,但是仿真的模型你要先确定好,不然和实际差很大。你现在200R+10nF大概是80kHz,

2、大概做了仿真,得到如图所示的电阻和电容的大小,电容容值太小,nF级别的,实际电路中,可能寄生电容都不止这么多。

------nF级别电容还算小,寄生电容一般都是pf级别。你如果觉得太小,减小电阻,增加电容量就是。

但是如果提高了电容值,那电阻值也会相应地提高,输出阻抗太大,会导下一级的电路驱动会受到影响。怎么权衡这个矛盾?

------截至频率的公式是 f=1/(2*pi*RC),你增加C保证f那应该减少R啊。至于你说阻抗变化,RC滤波输出阻抗等效是电阻并联电容,并联结果是比小的还小。何来阻抗太大,真的计较这点“大”那就要用跟随器。

谢谢!我这个就是跟随出来的,但是跟随出来的波形有过冲,才使用了这个RC.

谢谢,你说的是截止频率的公式么。

居然有大师在,1111111

你的下一级不是需要输出阻抗小吗?为什么Out加射随可以解决这个问题啊

学习!

过来学习

过来学习