求教一个运放电路工作原理

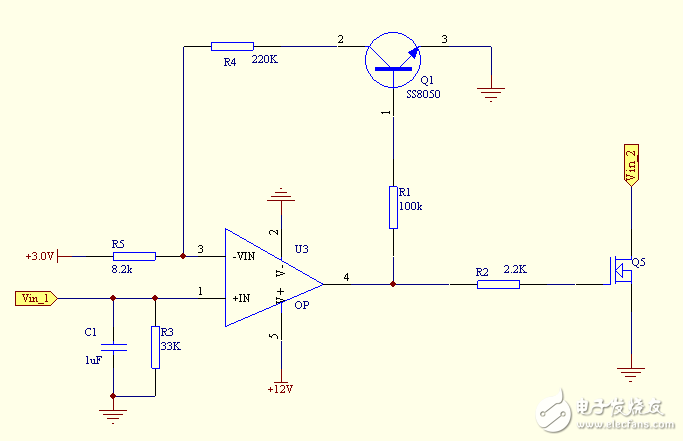

遇到一个运放电路,不知其工作原理,请各位指点一下,电路图如下:

测试输入输出电压在工作过程中变化:当Vin_1输入电压为0V时,Vout(第4脚)输出为0V;当Vin_1输入电压为2.6V时,Vout(第4脚)输出为3.9V,从这里来判断,这应该是一个比例运放电路,但不理解的是反馈环路中三极管Q1

在电路中的作用,即使输出为3.9V时,Q1依然是处于截止状态,反馈环路中的阻抗应该没有发生变化,那么运放输出怎么会发生变化呢?

我没实际测试也不知道我说的对不对 所以只是以我的思路的 仅供参考:

看见电路图第一反应是列节点电压方程求出输入输出关系 3/r5=ui/r5-uo*b/100k

uo=(100*ui-300)/r5*b

我列的节点电压方程不一定对 所以仅供参考

b是三极管放大系数 假设固定,ui是输入信号,uo是运放输出端输出电压不是mos管输出电压

好吧 我前面列列的是错误的算法

我无能为力了 看来看去看出的结果都是

uo=(100k*ui–300k)/r5*b

应该有个电压拐点

这貌似是【增益可调差动放大器】,具体可找一本运算的书籍看一看就知道了。计算公式都是现成的。

若觉得满意请采纳,谢谢!

电压比较器,没发现反馈电阻,三极管导通后会是反向端电压降低,同相端要比原来使其输出相同电压的输入电压要低一点,记忆中迟滞比较器符合

【当Vin_1输入电压为0V时,Vout(第4脚)输出为0V】,没错。

【当Vin_1输入电压为2.6V时,Vout(第4脚)输出为3.9V,从这里来判断,这应该是一个比例运放电路,......】,错了。输出仍为0V,而且不是比例运放电路。

这是通过附加一个三极管来构成的迟滞比较器。

该电路的优点是,选择确定它的上、下门限的手续简化,无须繁琐的计算,便于修改调试。

上门限按需选择,3.0V;下门限就是三极管导通状态下R2和R3的分压值,8.2k 和 220k,分压得 2.892V。

你确定三极管没导通吗?基极有电流了呀,是基极电流太小吗?

昨天夜里发了一个回帖,现在还未见审核通过。

迟疑比较器

不会不会吧

谢谢

我不知道公式 只知道 1脚同相输入 4脚高电平输出

Q5动作 Q1动作 3脚电位降低 约为2.89

使1脚不工作于临界状态 4脚保持稳定输出

hoa'

好啊

厉害看

是

无外于虚短与虚断吧。

http://www.analog.com/media/cn/t ... rials/MT-083_cn.pdf