关于复位电路的时序问题

时间:10-02

整理:3721RD

点击:

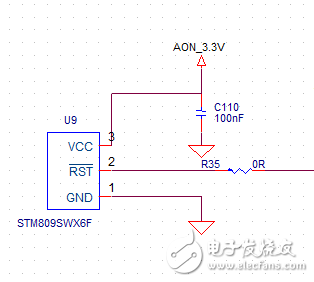

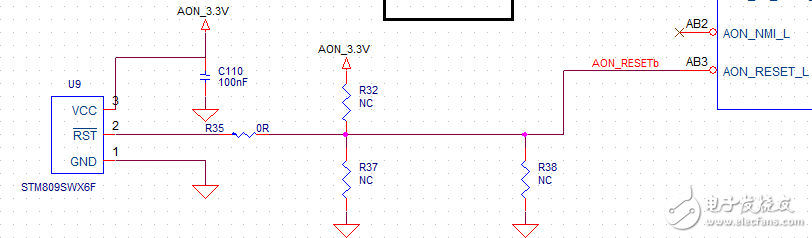

复位电路RST信号为什么与VCC信号需要保持一定的时间差? 复位电路使用复位芯片,电路图如下,求解答

电路图如上,RST信号是否代表低电平有效?

你可以看看STM809的手册,RST是低电平有效。在电源VCC超过RST的门限后,RST会输出低电平,保持一段时间。然后RST变高

很多单片机的上下电时序要求吧。VCC上电后,需要一段时间内部时钟稳定之类的,然后再给复位信号。

复位信号会一直有吗

电路图如上,RST信号是否代表低电平有效?

你可以看看STM809的手册,RST是低电平有效。在电源VCC超过RST的门限后,RST会输出低电平,保持一段时间。然后RST变高

你可以看看STM809的手册,RST是低电平有效。在电源VCC超过RST的门限后,RST会输出低电平,保持一段时间。然后RST变高

不好意思,刷屏了。

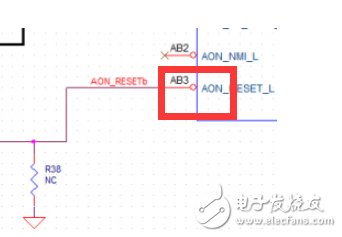

谢谢! 是不是这种管脚前带圆圈的都是表示该引脚是低电平有效呢?

是的,还有信号名称上面有横线的

好的,谢谢!

复位都是在低电平,延时一会儿吧。