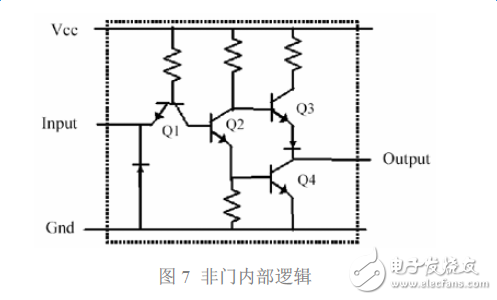

关于非门的问题想请教

错了,我们忽略了一个细节!非门内部逻辑图没有错。

输入高电平时,误以为发射结没有电位差,貌似Q1截止,其集电极开路,导致Q2截止,......,如此下去,错误地得到了同相输出的关系。

其实,此时左上角电阻与Q1集电结、Q2发射结、Q4发射结共同组成了一条顺向通路(四者串联节点处的电位可以大致估算出来,其中Q1的基极不等于电源电平,而应是2.xx伏,其发射结处于反向偏压,集电结处于正向偏压),Q2和Q4同时导通,Q3截止,输出低电平。反相关系。

输入低电平时,毫无疑问,Q1导通,Q2截止,故Q4截止,同时Q3获得基极注入电流而导通,通过二极管向负载输出高电平。也是反相关系。

没上拉也没下拉,怎么确定

菜鸟自顶

。

所谓高电平,即为等于或接近VCC。

发射极输入在VCC,基极无电流,电阻上无压降,所以基极和发射极同电位,同在VCC上,Q1截止。

这个Q2基极不会有电压的

那当输入为高电平时输出不还是高电平吗,我觉得是不是应该在Q2的基极加上拉呢?

你分析的输出的确如此 至于上拉电阻 感觉没有必要

Q1截止那Q1的集电极什么电平呢?哪个原理图会不会有错呢

这是我在一个资料中看到的,输入低电平输出是高电平,但输入如果是高电平,我感觉有点怪啊,前辈能不能分析下,谢谢哈

输入高电平,Q1截止,集电极相当于开路,不为Q2基极注入电流,故Q2截止,。

最后结果不是反相,是同相缓冲门啊!

补充内容 (2017-4-13 14:43):

错了,我们忽略了一个细节!电路没有错。

等下,重新发帖。

Q2应该有上拉电阻的呀,要不然怎么工作的?

哈哈,经你这么一说,才想起来,原来把集电结给忘记了,谢谢!

其实Q 2基极还有一种状态即开路悬浮状态,这时Q 2也是截止的。

你的意思是Q1截止时,发射极反偏,但集电结正偏,Q1的基极和集电极并没有断开,而是导通的,所以Q2的发射极并不是悬空的,这样理解对吗。我之前以为Q1截止,那么Q1的基极跟发射极和集电极都是相当于开路的状态

刚开始,我的错误思路是:

输入高电平时(所谓高电平,理论上等于或接近VCC),即Q1发射极输入在VCC上,基极无电流,电阻上无压降,所以基极和发射极同在VCC电平上,Q1截止,其集电极相当于悬空开路,不能为Q2基极注入电流,导致Q2截止,......,如此下去,错误地得出了同相输出的关系。

重新表述一下:

实际上,输入高电平(哪怕不十分接近VCC)时,Q1的发射结不会有正偏出现,或者仅有很小的正偏。这种情况下,发射结不起任何作用,就好像失效、不存在了一样。而其集电结却同(左上角的)基极电阻、Q2发射结、Q4发射结顺向串联,从VCC电源获得了正向偏置。正因为如此,正向偏置电流在基极电阻上产生了压降,基极电位下降,发射结才有了反偏!

没上拉也没下拉,怎么确定

你看下JQ_Lin 的解释