请问以太网phy的差分线为什么要接上拉电阻?请网络电路设计大牛指导

时间:10-02

整理:3721RD

点击:

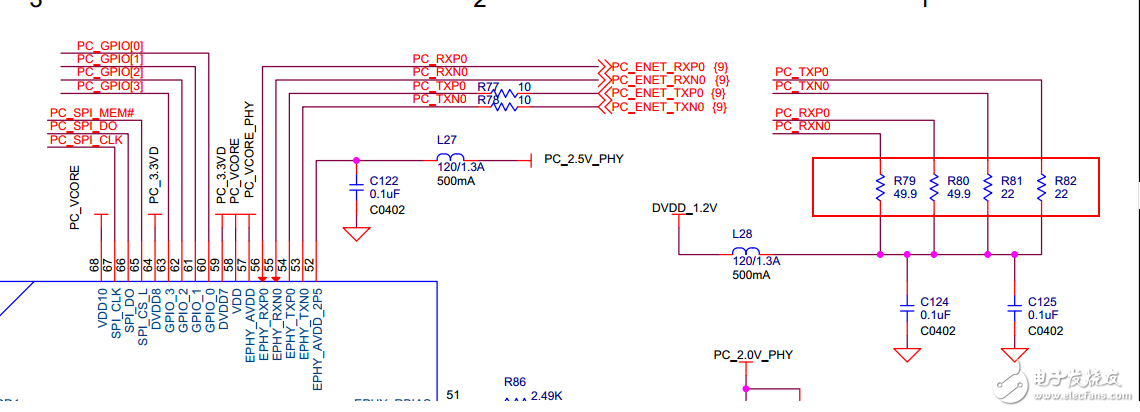

如图,请问这个电路图的以太网phy的差分线为什么要接上拉电阻?R79~R82。

因为上拉电阻很小,导致功耗很高。

是不是这个电路图有问题?

因为上拉电阻很小,导致功耗很高。

是不是这个电路图有问题?

小编可以查一查iic为何上拉电阻,原理应该一样!

你好,非常感谢你的回复,但是这个网络差分信号线不是开漏输出?所以用IIC的上拉来解释连接,ms没什么道理。

1. 我认为50欧姆是为了差分匹配用的,

2. 根据第一条,那两个22欧姆也应该换成50欧姆,

3. 0.1uf的接地电容是为了去耦,

4. 现在最不可理解的地方为什么还上拉到DVDD_1.2V?我觉得没什么必要吧?

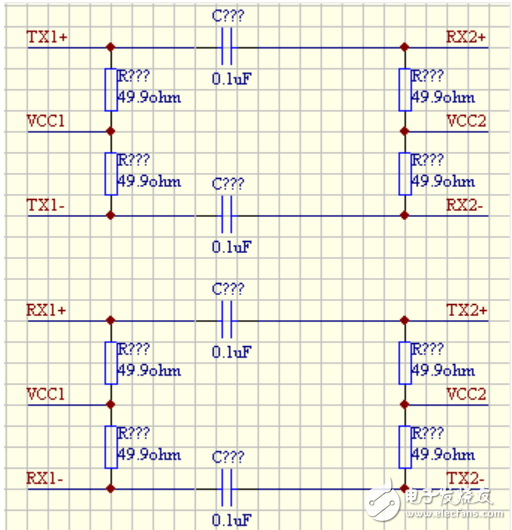

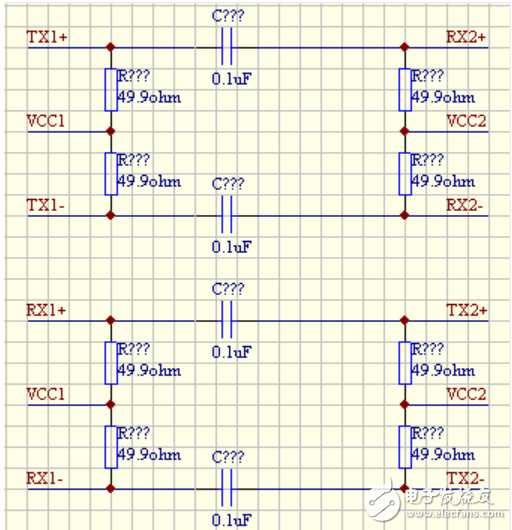

我来说一下背景,这个电路实际上两颗带phy的芯片,在板上不需要变压器进行直连的设计,所以需要串联0.1uF的电容,然后因为两颗芯片的phy都是电流型驱动,所以需要上拉电压以便提供足够的电流,电阻应该都是50欧姆,因为差分线路阻抗匹配是100欧姆,

可以参考 http://download.csdn.net/detail/s1987ea/9548378

我来说一下背景,这个电路实际上两颗带phy的芯片,在板上不需要变压器进行直连的设计,所以需要串联0.1uF的电容隔离,因为两颗芯片的phy都是电流型驱动,所以需要上拉以提供驱动电流,上拉电阻都应该是50欧姆,为了匹配差分线的100欧姆阻抗,有一个参考文档网上: http://download.csdn.net/detail/s1987ea/9548378