电子行业人士带你入行之封装小白篇

从设计到制作,经过一系列的流程后一颗IC芯片终于“诞生”了,接下来就是将其封装起来。但想要把它装到电路板上,确是一件费力的事。

目前电子元器件行业中,IC有两种常见的封装办法:一种是BGA封装(Ball Grid Array Package,球栅阵列封装),具体参照CPU的包装;另一种是DIP封装((DualIn-line Package,双列直插式封装技术),具体参考遥控玩具车的包装。

经久不衰的传统包装

作为最具历史的封装办法,DIP封装也是IC封装最早的技术,它是以金线将芯片接到金属接脚(看起来有点像条黑色的蜘蛛),成本低且适合小型的电子元器件芯片。但是这种办法因采用的是散热效果较差的塑料,所以只适合体积小、孔较少、对运作速度没那么高要求的IC芯片。

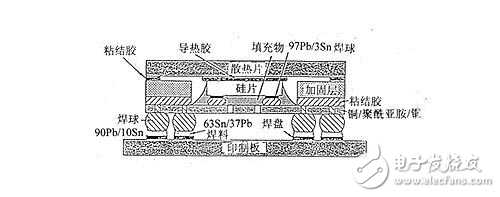

而BGA封装(球栅阵列封装技术)相比起DIP封装,则更为先进,它可以封装体积更小的IC芯片,以便将电子元器件放入体积更小的装置中。位于芯片下方的接脚位,可以容纳更多的金属接脚。BGA封装连接方法比较复杂且成本较高,因此只适用于量不大但单价高的产品上,如CPU。

新技术跃上封装舞台

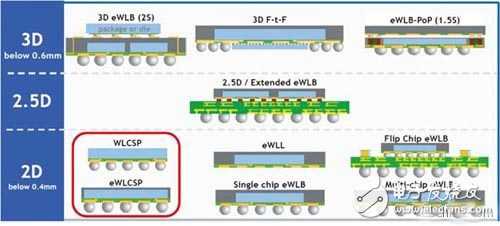

不管是DIP封装还是BGA封装,都会占用相当大的体积。IC芯片在发展,封装技术也一直在发展,现在越来越多穿戴装置、行动装置等,都需要相当数量的电子元器件,这些独立封装的元件在组合的时候,会耗费相当一部分的空间。针对这种问题,业内人士给出了两种缩减体积的办法:SiP(System In Packet)和SoC(System On Chip)。

SoC到底是个什么鬼?其实SoC就是将不同功能的IC整合到一颗芯片上,这样不仅能缩小芯片的体积,还能缩短电子元器件之间的距离,提高(芯片的)计算速度。方法则是在IC设计之初,将不同的IC摆放在一起,再通过一系列的设计流程做成一张光罩。

当然,SoC也并非是万能的。IC芯片在封装的时候,各有各的外部保护,间隔较远(才能达到减少对彼此的影响/干扰的效果)。但是将一定数量的IC封装在一起,不但会增加工程师的工作量,而且还会出现高频讯号影响其他IC的情况。

而且,IC(电子元器件)并非是你想封装在一起就能封装在一起的,这需要得到其他IC(intellectual property)厂商的知识产权授权。在封装的过程中,工程师们需要获得整个IP的设计细节和相关的技术,才能做出正确的光罩;这并非易事,要知道像苹果这样的巨头,也需要通过高薪挖人才能得到相关的电子元器件技术,才能设计出全新的IC。当然自行研发所需的成本也极大,建议企业还是量力而行吧。

SoC的补充方案—SiP

鉴于上诉SoC的种种缺点,SiP作为补充方案跃上整合芯片的舞台。SiP是通过购买各个厂商的IC后在最后一次封装起来。这个方案比起SoC少了IP授权,也就大幅度减少开发成本。由于购买的都是独立IC,所以讯号干扰的情况也大幅度降低。

关于SiP的著名案例,那就不得不提苹果的爱我去(IWatch)。体积较小的IWatch自然无法采用常规的封装技术,SoC过高的设计成本自然也非首选。怎么办?噔噔噔噔,可以缩小体积且高效融合各大IC/电子元器件的SiP成为可行的折中方案。

封装完成后,下一步就是测试阶段,这个阶段主要是测试封装后的IC及其电子元器件是否能正常运行,测试通过后便可出货给组装厂,做成市面上常见的电子产品。

谢谢大家的分享。

学习啦啦啦啦啦啦

学习了,谢谢小编。

学习学习,谢谢小编

感谢分享。

小编 厉害 ! 多谢分享

内容基础详细,点到位,赞!

谢谢大家的分享。