DDR2去耦电容问题

时间:10-02

整理:3721RD

点击:

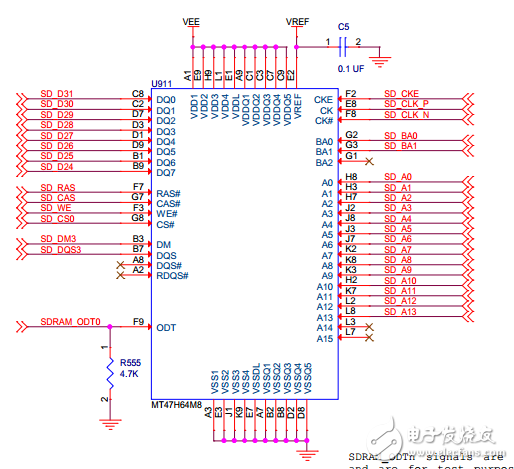

现在在画一个ColdFire54455的板子,DDR2去耦电容这里有几个不明白的问题,还望大家不吝赐教,万分感激。DDR2我用的是MT47H32M16,官方Demo原理图用的MT47H64M8,用了4片,每一片各10个管脚,四片共40个电源管脚,单片如图

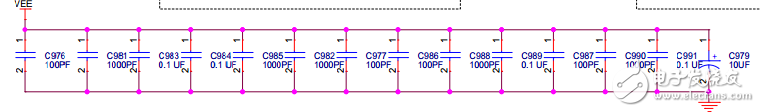

Demo给出的去耦电容一共十几个,貌似容值还有规律0.1u 0.1p 1p的各四组等 去耦电容如图

我的第一个问题是去耦电容 为什么要这么选择(容值,数量)、在PCB制作中,电容该如何给4片DDR分配,如何摆放。

其次,官方给的Demo中,还有42个终端电阻,终端电压也用了电容。终端电阻如图

通常。每一片DDR会配一个10uF电容,在总电源入口,每个电源管教要放置如你所写一组电容,目的就是消除DDR的工频和谐波干扰进入电源网络。(为了EMC),

第二个问题,终端电压VTT和终端电阻,只能说明处理器好差劲,OD输出玩DDR2?坑爹啊。这不是明显给layout工程师添堵么?终端电阻51ohm目的是阻抗匹配,当控制器OD输出高电平时,DDR从VTT取电流,电流可以通过匹配的网络流入DDR2减少纹波电流。

DDR2的技术已经非常成熟,实际应用时,一般每个电源脚放一个0.1uF+10nF就足够了,很少会再摆更多退耦电容,因为你这么摆放,直接就把完整地平面搞的乱七八糟了!DDR2是最好以4层板为基础,电源滤波和芯片顶层。2,4层走信号。3层完整地。时钟差分信号走底层

一切以参考设计为和DDR设计指引为参考吧!

Demo给出的去耦电容一共十几个,貌似容值还有规律0.1u 0.1p 1p的各四组等 去耦电容如图

我的第一个问题是去耦电容 为什么要这么选择(容值,数量)、在PCB制作中,电容该如何给4片DDR分配,如何摆放。

其次,官方给的Demo中,还有42个终端电阻,终端电压也用了电容。终端电阻如图

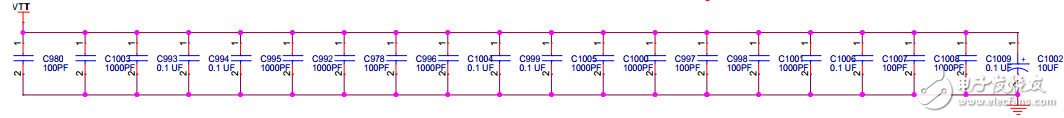

终端电压上连接的电容图为

我的第二个问题是终端电压上的电容该如何分配,PCB中如何摆放。

这个倒是见过都是采用并列 紧密方式排板的 至于为什么感觉是仿真用一个大电容而引起的谐振详细 (这个是个人推测)

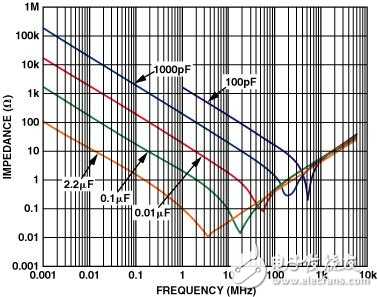

第一个问题:

要看下面这个经典的图,由于电容的寄生参数,每个电容都有工作频率范围,超过这个频率,电容就不再是"电容"了.因此出现了需要0.1uf,100pf,1pf等多个电容并联的状况。

通常。每一片DDR会配一个10uF电容,在总电源入口,每个电源管教要放置如你所写一组电容,目的就是消除DDR的工频和谐波干扰进入电源网络。(为了EMC),

第二个问题,终端电压VTT和终端电阻,只能说明处理器好差劲,OD输出玩DDR2?坑爹啊。这不是明显给layout工程师添堵么?终端电阻51ohm目的是阻抗匹配,当控制器OD输出高电平时,DDR从VTT取电流,电流可以通过匹配的网络流入DDR2减少纹波电流。

DDR2的技术已经非常成熟,实际应用时,一般每个电源脚放一个0.1uF+10nF就足够了,很少会再摆更多退耦电容,因为你这么摆放,直接就把完整地平面搞的乱七八糟了!DDR2是最好以4层板为基础,电源滤波和芯片顶层。2,4层走信号。3层完整地。时钟差分信号走底层

一切以参考设计为和DDR设计指引为参考吧!

我明白你跟我解答的第一个问题,不同容值的电容是为了滤不同频率的干扰。可能我没说明白,我的问题是:四片DDR2,共40个电源脚,可是只用到了13个去耦电容,并不是每个电源引脚分配一个。我纳闷儿的问题就是这个,按理说不应该每个电源引脚都有去耦电容么?

还有终端电阻的作用应该就是阻抗匹配,消耗信号回波反射的,处理器不是OD输出,因为我们上一版的SDRAM用的DDR1,没有用终端电阻,进而也没有这个终端电压。这次用DDR2参考的是官方的Demo,加了这些终端电阻,和终端电压的去耦电容。我很费解,以前没接触过DDR2电路的设计。

如果是这样,你看下原厂给的PCB参考设计的电容摆法,一个芯片最多也就摆10个电容差不多了,再多了真摆不下。可能是原厂经验够强大,沿着电源方向逐渐减少了电容容量。