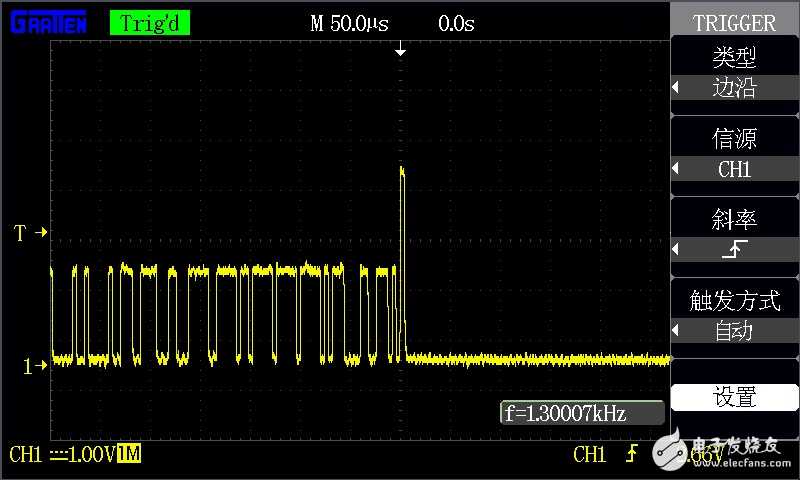

CAN总线测试,示波器测量差分信号波形发现应答位电平偏高很多,这个是怎么回事,有何影响,如何处理?

时间:10-02

整理:3721RD

点击:

补充说明:测试环境,29个模块手牵手连接(用的是普通网线的一对双绞线接的CANH和CANL,另外模块供电24V,用的两根网线并联做电源线),线两端各接120欧电阻,通讯能够正常,只是测量波形时发现应答位电平偏高很多,模块少一点相对会低一点,仅当只有两个模块时应答位电平才和正常数据显性电平一制,不知道这个是怎么产生的,会不会影响到通讯或芯片寿命。

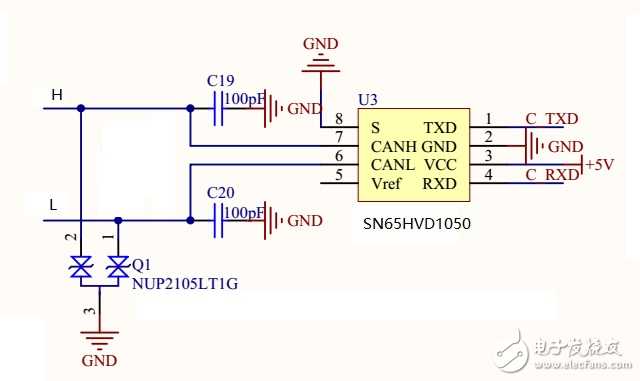

下图附示波器波形和模块总线接口部分原理图,CAN收发器用的TI的芯片

下图附示波器波形和模块总线接口部分原理图,CAN收发器用的TI的芯片

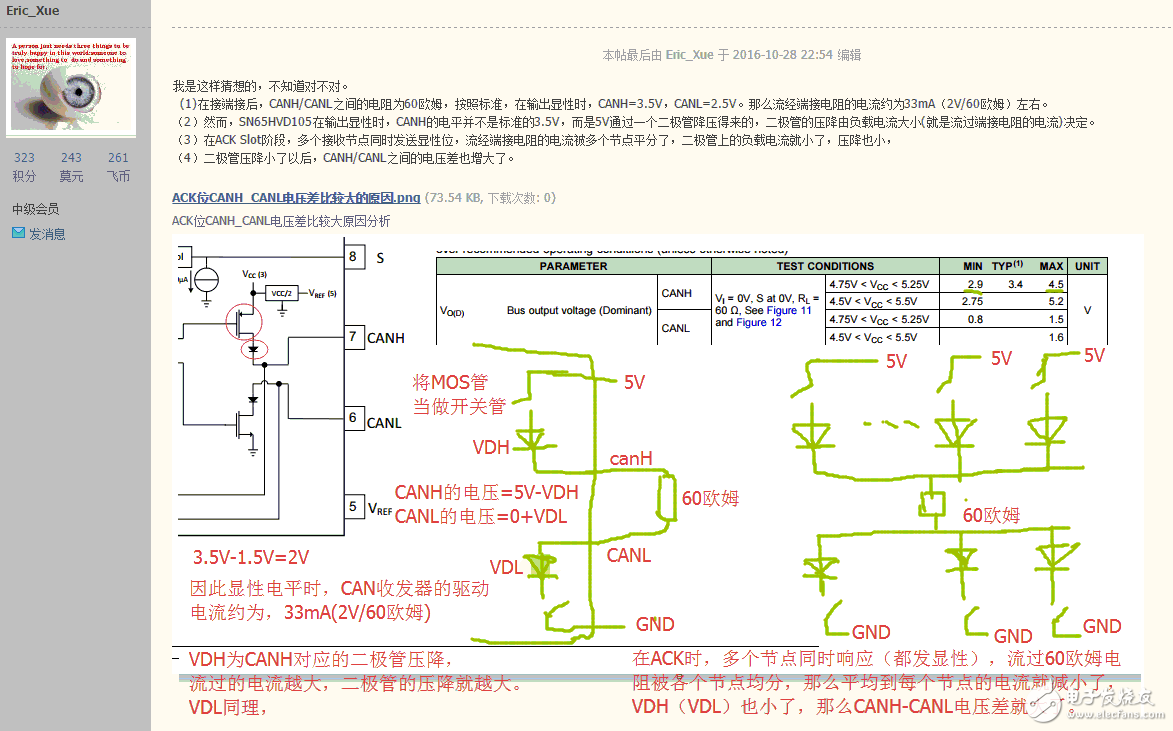

来自阿莫论坛的回答,觉得分析的有道理

我认为产生的原因是U3的输入电平驱动太强,造成应答信号串入U3内部造成,当应答模块少时,应答信号的驱动能力较弱,U3内部的保护电路能够吸收这个高电平,故显正常。

Q1只是解决高压脉冲吸收问题,对这个问题不起作用。

解决问题的要点是保证U3和模块的电平衔接问题,或者通过串入电阻来削弱模块的驱动能力,或者让各个模块的应答不要同时出现。

我认为这样的冲击对U3不好。