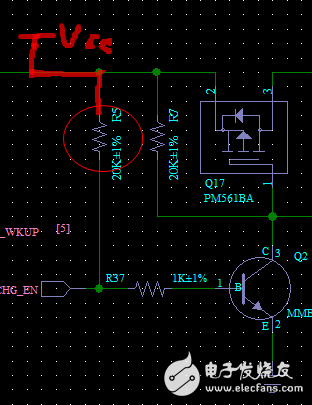

为什么要接上拉电阻R5?

时间:10-02

整理:3721RD

点击:

接上拉电阻R5是因为芯片IO口开漏输出要求吗?还有没有其他原因?

。不太清楚 求大神解释

IO接上拉电阻增加驱动能力的,防止负载过大,将高低平信号拉低。

驱动能力不够,所以加上拉,可以驱得动三极管

你可以不加电阻试试啊,减少外部电平的干扰

可能这个IO口 没有上拉功能 ,所以关IO口即可保持高电位,开IO口为低电位

有两种考虑

1、上电瞬间,就需要开启Q17

2、如你所说,芯片IO内部没有上拉

另外这个电路需要注意,你控制器IO口,需要能够耐Vcc的电压。 Q17的VGS耐压要满足Vcc电压。

所以,一般,io口上拉是用控制器的供电,而Q17 会用电阻分压。

感谢坛友们热心的回复

感谢柠檬守护支持的

增加驱动能力