高速PCB设计系列基础知识13|原理图走线与设计步骤

时间:10-02

整理:3721RD

点击:

上期讲到了高速PCB设计中建立元件库的方法

元件放置完成后

接下来的重点便是连接走线

▼▼

原理图走线

▼▼

在原理图走线中有导线的连接和总线的连接。

执行Place指令下的操作,可以用以添加连线(Wire)、总线(Bus)、模块(Hierarchical Block)及其输入/输出端口(Hierarchical Port)、标题栏(Title Block)、页面连接器(Off-Page Connector)、网络名(Net Alias)等原理图所需工具。

走线完便是

▼▼

层次原理图设计

▼▼

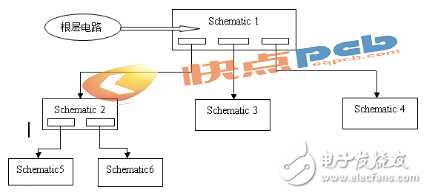

1、层次原理图,设计结构如下图:

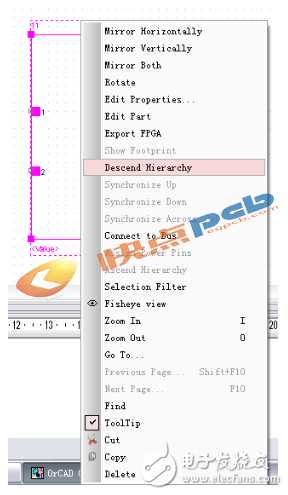

2、放置层次框图及引脚

3、右击该Hierarchical Block,执行De scend Hierarchy命令,则可进入层次框图的下级原理图绘制界面,而后进行该Hierarchical Block的下层电路设计页面

当在Capture CIS中完成原理图设计后

需要对原理图进行后续处理

因此下期我们将详细介绍

原理图后处理具体操作

请同学们持续关注【快点PCB学院】公众号

感谢小编分享 小编能否打包上传呀 这个样看着不连贯的

全部分享完会打包的,别担心~~可关注【快点PCB学院】公众号,看技术贴更便利

最近手机废了 改天吧

过来看看!学习学习。

谢谢小编

11