资深工程师谈晶体管使用心得:用晶体管来实现功率负载的控制

作者:Mountain 毕业于燕山大学,获学士学位。工作5年多,一直从事医疗检测及分析仪器设备相关的硬件电路设计工作。

最初接到李老师的邀请要写一篇晶体管使用心得的时候,内心着实惶恐了一阵,毕竟才疏学浅,至今还徘徊在模拟电路的大门外。但又转过头一想,是晶体管的使用心得,而不是《晶体管电路设计》上册当中讲到的那些内容。例如基本的共射极电路、共集电极电路、共基极电路的电路分析,又或者引起晶体管频率特性变化的密勒效应,再比如基于晶体管的负反馈、差分放大电路的设计。这些内容如果认真的去看《晶体管电路设计》,同时结合李老师的电路板进行实际的电路搭建和测试分析,相信每一个位用心的同学都会有或多或少的收获。

还是回到这篇文章的主题,晶体管的使用心得。由于本人所从事行业的限制,基本没有机会像《晶体管电路设计》书中那样深入的使用晶体管来搭建电路,而更多的是使用晶体管来实现功率负载的控制,还有配合运放或者其它集成电路来实现一些常见的功能,如扩流、恒流、稳压等。本文也就正是基于这方面,和大家分享一下晶体管的使用心得,希望能对初学者有一定的帮助,老司机可以直接忽略在下的班门弄斧了。

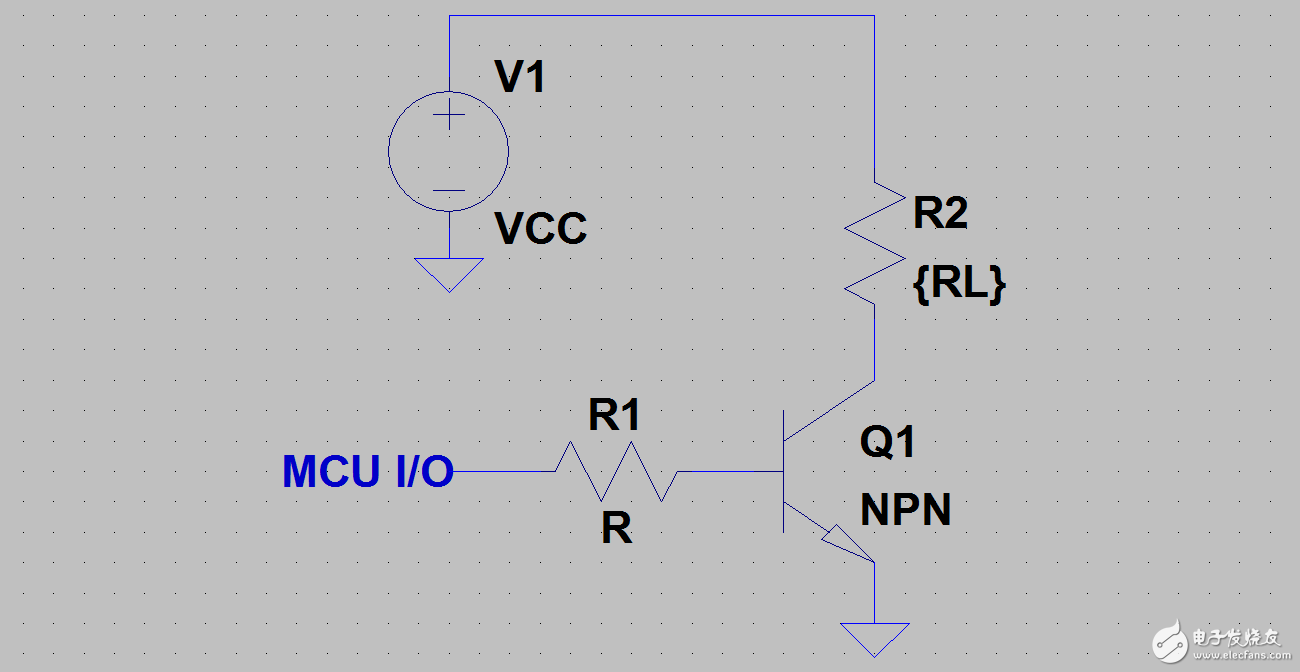

首先来看一个负载控制的实例,电路中以“{RL}”来替代负载。通过单片机的I/O来方便的控制负载通断电,图1所示的电路简单明了,使用一个NPN晶体管,高电压平通,低电平断。但再仔细想想,好像没有表面上的那么简单,至少需要考虑到以下几个因素:

流入晶体管基极电流的大小,取决于负载电流和hFE( DC Current Gain);

晶体管的电大允许通过电流,取决于IC( Collector Current - Continuous);

晶体管集电极的电大耐压值,取决于VCEO(Collector-Emitter Voltage);

晶体管能承受的最大功耗,取决于PD(Total Device Dissipation)。

图1一个NPN控制负载

仅针对上面提到的四个因素,其中任何一个不合适,都会导致电路不能正常的运行,甚至烧毁晶体管。因此很多时候是我们把复杂的事情简单化,或是疏忽,或者没有足够的能力看清它,而只有当它“东窗事发”的时候才会引起我们足够的重视。

上面的实现方式是用一个NPN来实现的,如果现在要求换成是用一个PNP呢?还能这么“简单”的实现吗?答案是否定的,因为很多时候负载的供电电压要明显高于单片机的供电电压,即使是在负载5V供电,单片机3.3V供电的时候,只用一个PNP也会出现不能关断负载的问题(Why?)。那这时候常见的解决办法是再加入一个NPN晶体管,如图2所示。图1和图2也就够成了常见的低压侧、高压侧的开关控制电路。有了前面的这些基础,下面再加入一个新的电路需求,用晶体管实现过流保护电路。感兴趣的同学可以先不要往下看,自己在脑海中想一想,看看有没有火花迸出来。

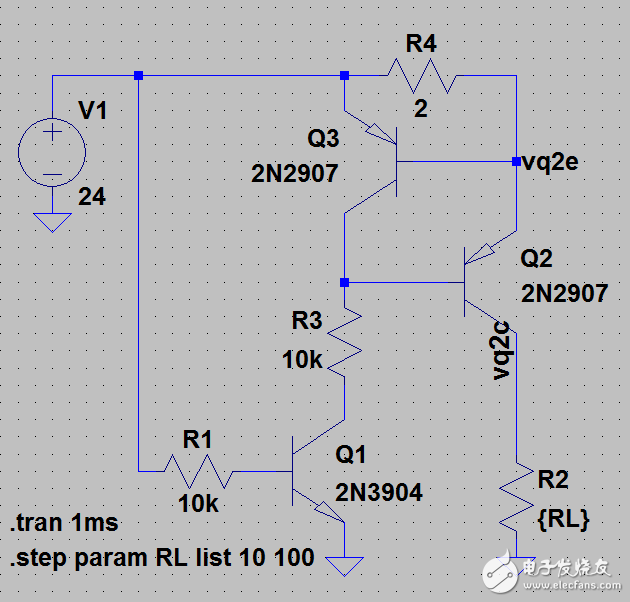

图2一个PNP、NPN控制负载

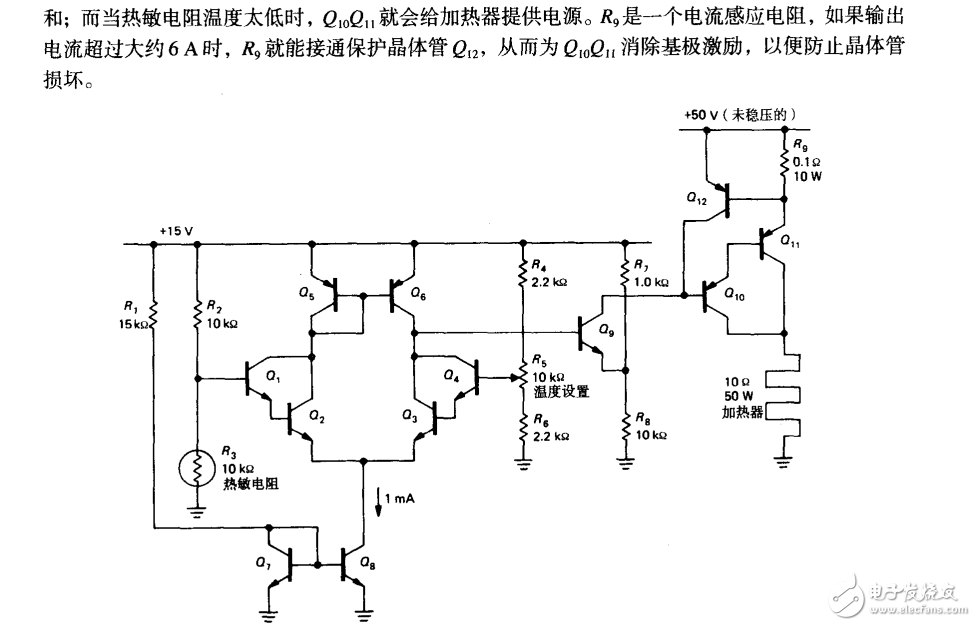

图3《电子学》2.5.2温度控制器

三年前看《电子学》的时候,里面有一个温度控制器涉及到“过流”保护(当时认为是过流保护),如图3所示,书中给出的解释比较简单,但似乎也有道理。那时还把这部分电路进行了仿真,但没有得到想要的结果,最后不了了之。现在再把这个输出部分的电路单独拿出来分析一下,看看到底是不是如书中解释的那样。由于图中的电路是用于进行线性放大控制,而这里只需要开关通断控制,因此也对电路进行了一些调整,如图4所示。

为了方便仿真,控制端直接接到了负载电源24V的电压上,也就是一上电压负载就应该导通。图中使用的晶体管只是LTspice仿真模型库当中现成的模型,没有什么特殊的型号要求,并用一个PNP晶体管替代了图3中的两个PNP管构成的Darlington管。“.tran 1ms”是用来执行上电以后1ms时间内的瞬态分析,“.step param RL list 10 100”是用来仿真当负载电阻分别10和100欧姆时的电路工作情况。

下面来简单的分析一下这个电路的工作过程,由于Q3的加入,当R4的电压压降超过0.6V的时候,Q3会导通,Q3的集电极会被拉高,也就是《电子学》当中的“消除基极激励”效果。这个消除基极激励,是指完全消除Q2的基极激励?Q3导通,其集电极电压接近24V,使得Q2截止?还是只能消除Q2的集电极电流达到使Q3导通的电流以后,继续进一步增大的基极激励?有些拗口,但值得仔细想想。

图4简单的“过流”保护电路

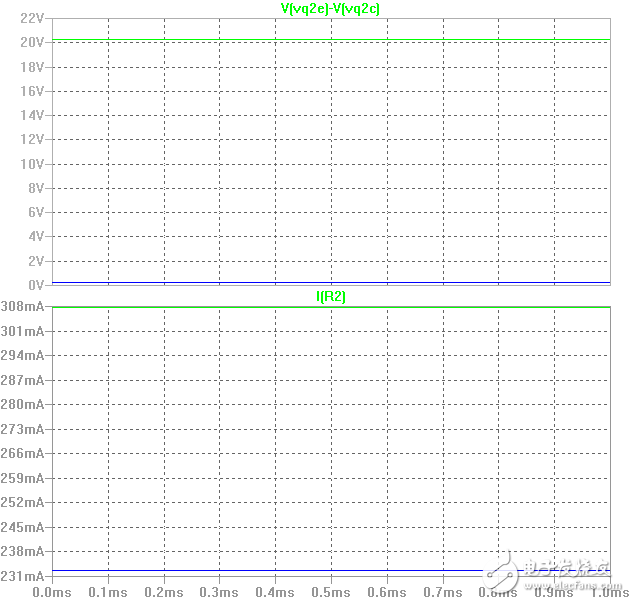

公布答案,仿真结果如图5所示,蓝色的负载电流的仿真结果对应负载为100欧姆的情况,电流大概为230ma,R4上的压降为0.46V,Q3没有导通。绿色的负载电流的仿真结果对应负载为10欧姆的情况,电流大概为310ma,R4上的压降为0.62V,此时Q3已经导通,并起到了一定的“过流”保护作用。此时即使负载电阻进一步减小,流过负载的电流也不会明显增大,基本维持在310ma左右,其实是晶体管的基极和发射极之间的导通电压维持在0.6V左右。Q3的导通真的消除了Q2的基极激励了吗?好像并没有,对不对?!

这个“过流”保护电路的关键就是晶体管的基极和发射极之间的导通电压,为了简单分析通常取0.6V进行计算。正是这个0.6V对晶体管电路的分析和设计起到了很重要的作用,因此要牢记在心并达到灵活应用。

再来看一下如果没有Q3,当电路中的负载为1欧姆近似于短路的时候,电路中流过的电流肯定要远远大于310ma。虽然Q3的加入起到了“过流”保护的作用,但实际使用图4所示电路的时候是没有任何实际意义的。因为当负载因短路或其它原因引起过小时,Q2的发射极和集电极之间的电压会很大,如图5仿真结果曲线“V(vq2e)-V(vq2c)”所示,此时Q2上的功耗会很容易超过其允许随承受的最大功耗,并导致其烧毁。因此图4不是真正意义上的过流保护电路,即在超过一定的电流以后自动关断电路或者进入打嗝模式,而将其称之为限流保护电路则更为合适。

图5简单的过流保护电路仿真结果

那能不能在图4的基础上,靠加入NPN或者PNP来实现真正意义上的过流保护电路呢?这个问题留给感兴趣的同学思考,这里不再深入展开。

至此,随着前面三个简单电路的分析,引出了在使用晶体管的过程中基本需要注意的几个主要因素:

hFE( DC Current Gain);

IC( Collector Current - Continuous);

VCEO(Collector-Emitter Voltage);

PD(Total Device Dissipation);

VBE(Base-Emitter Voltage)。

在分析或者设计需要用到晶体管电路的时候,多问问自己晶体管的集电极电流有多大,基极电流需要多大,它的最大功耗是多少,基极-发射极的电压是多大,晶体管什么是导通的,什么时候是截止的,随着前级输入信号的变化晶体管是趋向于饱和还是截止,然后又给后级电路带来哪些影响,也许会收到事半功倍的效果。

很多时候纸上得来终觉浅,而有些时候仿真也会和实际情况相差甚多,这时实实在在的电路总是能让我们的困惑迎刃而解。在以前这能只能通过面包板或者万能板,再加上若干元器件来实现。而现在李老师的努力下,让我们有了一种全新实践动手搭建电路、测试电路的方式,即眼下如火如荼在聚丰众筹进行的“晶体管电路的实验艺术”的众筹项目,此项目将《晶体管电路设计(上册)》中的电路做成了电路实验板。针对每一章节内容中的电路,都有相应的电路实验板,焊接元器件,接上相应的信号源,用示波器测试电压波形,书上内容活灵活现的展现在了眼前。透彻理解晶体管,这一切都变得简单了很多。有没有心动,那就快来聚丰众筹报名参加吧!

扫描二维码参与或戳这里

最后发个福利:

凡是转发本文的朋友均可参与抽奖,将送出十本《晶体管电路设计(上册)》图书(包邮)。

参与方式:发送朋友圈截图给李宁, 微信号:17717546924,注明“晶体管”

每周周一晚上9点,抽出十个名额。日期分别是5月30日,6月6日,6月13日,6月20日,6月27日,总共送出50本。

谢谢作者:Mountain 的分亨。