关于CPU的I/O接到其他芯片的配置脚的设计方式

时间:10-02

整理:3721RD

点击:

请教大家一个问题:做电路原理图设计时,CPU的I/O接到其他芯片的配置引脚时一般采用何种设计方式?有何设计规则?

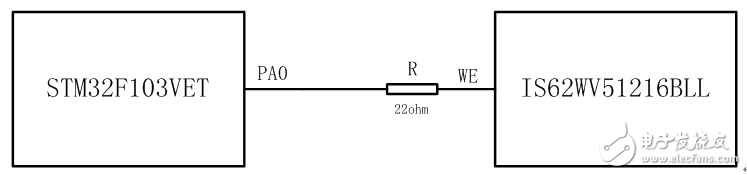

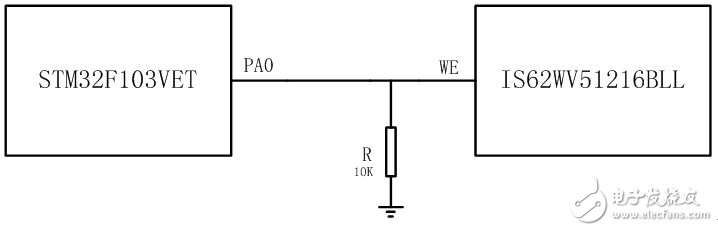

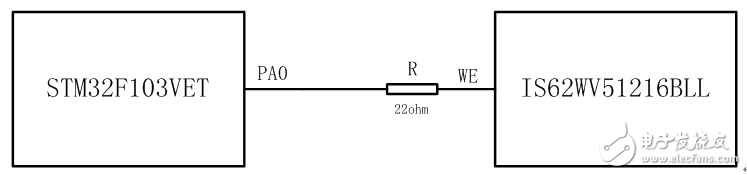

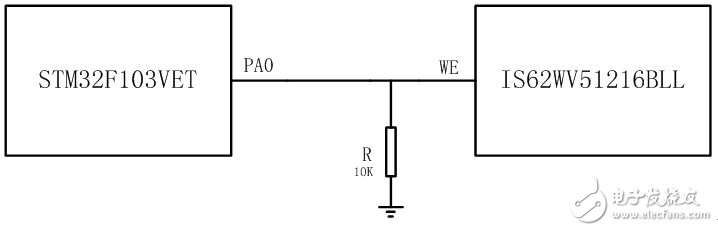

例:STM32F103VET的I/O接到一款SRAM(IS62WV51216BLL)的配置脚(WE, CS1, OE, LB, UB)上,I/O为配置脚提供高或低两种状态,以下两种方式是否合理或有无相关设计资料可供参考?

1)中间串入电阻,用于限流?

2)配置脚前下拉电阻

例:STM32F103VET的I/O接到一款SRAM(IS62WV51216BLL)的配置脚(WE, CS1, OE, LB, UB)上,I/O为配置脚提供高或低两种状态,以下两种方式是否合理或有无相关设计资料可供参考?

1)中间串入电阻,用于限流?

2)配置脚前下拉电阻

第一种电阻是减小信号过冲的,一般在100欧姆一下,多为22欧姆

第二种要参考SRAM的需求,下拉保证的是在CPU未配置情况下为低,配置之后按CPU输出来。这种电阻一般用10K左右

芯片之间的I/O连接要确保只有一个输出,否则电平冲突会造成芯片损坏

no answer,

又思考了一下,个人认为应是这样的:

如芯片手册中对配置脚有特殊要求(如要求下拉电阻等),则按照芯片手册要求来设计,如无具体要求,则直接相连即可。不过考虑到后面板级调试,还是建议在I/O 和 配置脚间加一个0ohm或小阻值电阻。

上拉电阻和下拉电阻把

谢谢,芯片之间I/O状态冲突的问题是由软件决定的吧?请问硬件设计时需要特别处理吗?

是软件决定的,硬件设计时在不确定的信号 引脚多放0欧电阻保证设计有误时能进行修改。同时多跟软件设计人员沟通

明白了,谢谢。