示波器重要“关键指标”——测量精确度/信号完整性

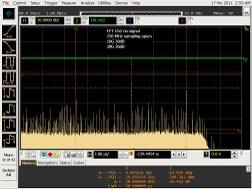

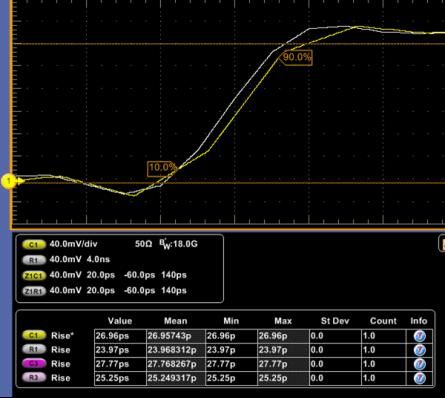

我们为此种前端设计提供的另一项创新是大偏移范围和终端性能。通过前置放大器芯片上的分离路径输入结构和多芯片模块上的 AC -接地端接电阻器,从而实现了此种性能。该性能可以更加轻松地对大型直流偏置或直流偏置终端信号做出准确的测量。 由于实现了向8HP的转换,DPO/DSA73304D示波器可以提供卓越的信号采集性能和分析能力。它帮助设计人员利用全部四通道前所未有的捕获功能够捕捉实时信号,并且利用业界最高的波形捕获能力捕获更多信号细节。利用一套工具集(为提供更快的设计和一致性测试而设计)实现设置、高速串行数据设计的捕获及分析的自动化。主要性能包括: · 双通道高达 33 GHz 和 100 GS / s,所有四通道 > 20 GHz 和 50 GS / s · 小于9 ps的上升时间(通常为 20/80) · 低于 0.56% 的垂直噪声,≥5.5 的有效位数 · 30 多个可定制特殊应用软件分析包 示波器性能因素 由于示波器是设计方面(尤其是信号完整性方面)至关重要的工具,设计人员应熟悉示波器指标以及它们影响测量的方式。让我们观察一下最重要的三大因素 - 上升时间、采样率和带宽 – 从而对它们进行更深入的了解。 此示波器的上升时间越快,测量到的上升时间会越准确。但是,当示波器的带宽或上升时间和信号的上升时间彼此更接近时,会怎样呢? 有人曾用经验法则(如:0.35/上升时间)来计算所需的示波器带宽,但这种经验法则只适用于某些示波器的前端设计,并且通常不适用于为高速串行数据速率和伴随的快速上升时间而优化过的当今前端设计。 应当注意的是,具有相同带宽性能的两台示波器可以具有完全不同的上升时间、振幅和相位响应。所以,仅了解示波器的带宽无法可靠地揭示出其测量性能。此外,通过计算确定的上升时间可能也不准确。了解示波器上升和下降时间响应的最可靠方法是使用一个理想的阶跃信号对其进行测量,该理想的阶跃信号比被测示波器信号快很多。 在使用 DPO/DSA73304D 的情况下,使用这种方法确定 9 ps 的上升时间。但是,信号速度可以被测量的意思是什么呢?根据正确的经验法则,信号上升时间与示波器上升时间的比值为 2x 或 >18 ps。事实证明,对于当今最快的 FPGA 设计中使用的28 Gb / s的串行解串器(SerDes)而言,这是指定的上升时间。 接下来,让我们看看另一个关键性能因素——示波器的实时采样率。因为更快的采样率带来更多的波形细节,所以这一因素非常重要。另一方面,对最快的信号而言,采样率不足可能会导致欠采样。此 DPO/DSA73304D 提供一流领先的采样率性能。利用交错技术提供采样率性能,此种交错技术使用 8 路采样/保持方法,将杂散高频的影响降至最低。参见以下数据,可得出被成功和失败执行的交错技术的差异: 成功的交错,频率杂散较少 失败的交错,频率杂散且有噪声 奈奎斯特定理(Nyquist theorem)指出,采样系统应对输入信号的最高频率采样 2 次以上。虽然这是最低起始点,但是在任何情况下,采样率越高,结果越准确。通过使用 2.5 倍较高采样率,此输入频率或更多输入频率可提供被关注信号上的更多采样点,且避免混叠。对于极高速信号表征而言,这是特别重要的。 下图显示了较高的采样率值。**跟踪线(C1)在 50 GS / s 上,而白色跟踪线(R1)在 100 GS / s 上。过采样原因包括: · 为确保信号中已知和未知的高频部分被捕获,且没有混叠 · 为实现卓越的定时分辨率(特别是快速瞬态信号或边缘上的定时分辨率) · 作为一种减少测量中噪音的手段。采样过密会减少量化噪声,产生的此类量化噪声是示波器中 A 向 D 转换的一部分 在此带宽前端,示波器必须有足够的带宽来捕捉高频部分,以便准确地显示信号的转换。 然而,当销售商为带宽需求进行善意提示,推荐 5 次谐波时,事情在不断发生变化。边沿速率(上升/下降时间)的变化并没有与数据速率的变化同步。这意味着,所需的最大带宽受到上升时间的影响更大。例如,目前第三代规格的上升时间在 30ps 的范围内。随着速率的不断提高,这似乎并没有很大变化,这表明,相对于

- 述评SPARQ系列网络分析仪之二:信号完整性问题与S参数的关系(07-28)

- 如何用示波器测量4个以上通道的信号(03-29)

- 初级工程师如何正确的使用示波器测量纹波(11-28)