协处理器及其他指令之:协处理器指令

指定协处理器执行的操作码,确定哪一个协处理器指令将被执行。通常与<opcode_1>令将被执行。通常与<opcode_1>配合使用。

3.指令操作的伪代码

指令操作的伪代码如下面程序段所示。

If ConditionPassed{cond} then

Coprocessor[cp_num]-dependent operation

| | 注意 | CDP指令通常被用来初始化协处理器。比如在作浮点运算操作时,使用CDP指令初始化协处理器寄存器。 |

4.指令举例

对协处理器P15进行操作。第一操作数opcode_1=2,第二操作数opcode_2=4,目标寄存器为协处理器寄存器c12,源寄存器分别为协处理器寄存器c10和c3。

CDP p15,2,c12,c10,c3,4

5.指令的使用

· CDP指令一般用于初始化协处理器,对ARM寄存器和存储器没有任何影响。

· 指令的编码格式中,bits[31∶24]、bits[11∶8]和bit[4]为ARM体系结构定义。其他域由各生产商定义。

· 硬件协处理器支持与否完全由生产商定义,某款ARM芯片中,是否支持协处理器或支持哪个协处理器与ARM版本无关。生产商可以选择实现部分协处理器指令或者完全不支持协处理器。

9.1.2 协处理器数据读取指令LDC

1.指令编码格式

LDC(Load Coprocessor)指令通过一定的寻址模式从一系列连续的内存单元将数据读取到协处理器的寄存器中。如果协处理器不能成功地执行操作,将产生未定义的指令异常中断。

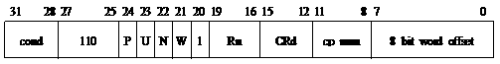

指令的编码格式如图9.2所示。

图9.2 LDC指令编码格式

2.指令的语法格式

LDC{<cond>}{L} <coproc>,<CRd>,<addressing_mode>

LDC2{L} <coproc>,<CRd>,<addressing_mode>

① <cond>

为指令编码中的条件域。它指示指令在什么条件下执行。当<cond>忽略时,指令为无条件执行(cond=AL(Alway))。

② LDC2

协处理器数据读取指令LDC的一种特殊格式。这种格式中指定编码的条件域<cond>为ob1111。这种设计为协处理器的设计者提供了一个灵活的扩展空间。此指令只能无条件执行。

③ <coproc>

指定协处理器的编号,标准的协处理器的名字为p0、p1、…、p15。

④ L

长读取操作指示域。设置指令编码格式中的Nbit(bit[22]),如果该位设置为1,说明指令是一个长读取指令;该位为0,说明指令为短读取指令。该指令常用于双精度数据传送。

⑤ <CRd>

确定协处理器目的寄存器。

⑥ <addressing_mode>

确定指令的寻址方式。它将指定指令编码格式中的P、U、Rn、W和8_bit_word_offset域。

3.指令操作的伪代码

指令操作的伪代码如下面程序段所示。

If ConditionPassed{cond} then

Address=start_address

load Memory[address,4] for Coprocess[cp_num]

while {NotFinished{Conprocess[cp_num]}}

address=address+4

load Memory[address,4] for Coprocessor[cp_num]

assert address==end_address

4.指令举例

(1)将数据从内存传送到协处理器p6寄存器c1中,使用寄存器寻址模式,将内存地址放到ARM寄存器r4中。

LDC p6,CR1,[r4]

(2)将数据从内存传送到协处理器p6寄存器c4中,使用寄存器变址寻址。

LDC p6,CR4,[r2,#4]

5.指令的使用

· 指令的编码格式中,bits[31∶23]、bits[21∶16]和bits[11∶0]为ARM体系结构定义。其他域由各生产商定义。

· 协处理器数据读取指令忽略地址后两位。如果系统中定义了系统控制协处理器,而且地址对齐检测使能打开,当地址bits[1∶0]!=0b00时,产生地址对齐异常。

· 硬件协处理器支持与否完全由生产商定义,某款ARM芯片中,是否支持协处理器或支持哪个协处理器与ARM版本无关。生产商可以选择实现部分协处理器指令或者完全不支持协处理器。

· 指令中字的传送数目由协处理器控制。ARM将连续产生后续地址,直到协处理器指示传送应该结束。在数据传送过程中,ARM将不影响中断请求,所以协处理器设计者应该注意不应因为传送非常长的数据而损坏系统的中断响应时间。

9.1.3 协处理器数据写入指令STC

1.指令编码格式

STC(Store Coprocessor)指令通过一定的寻址模式将协处理器寄存器中的数据存储到一系列连续的内存单元中。如果协处理器不能成功地执行操作,将产生未定义的指令异常中断。

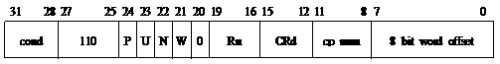

指令的编码格式如图9.3所示。

图9.3 STC指令编码格式

2.指令的语法格式

STC{<cond>}{L} <coproc>,<CRd>,<addressing_mode>

STC2{L} <coproc>,<CRd>,<addressing_mode>

① <cond>

为指令编码中的条件域。它指示指令在什么条件下执行。当<cond> 为指令编码中的条

- 实时操作系统软件调度器/硬件调度器的设计与实现(03-27)

- BASIC在PLC控制系统中的应用(08-15)

- 协处理器及其他指令之:零计数指令CLZ(08-13)

- 协处理器及其他指令之:交换指令(08-13)

- 协处理器及其他指令之:状态寄存器访问指令(08-13)

- 高效的C编程之: 浮点运算(08-30)