ARM指令寻址方式之: 内存访问指令寻址

4.2.5 协处理器Load/Store寻址方式

协处理器Load/Store指令的语法格式如下。

<opcode>{<cond>}{L} <coproc>,<CRd>,<addressing_mode>

表4.9显示了该类指令的寻址方式。

表4.9 协处理器Load/Store指令寻址方式

|

| 格 式 | 说 明 |

| 1 | [<Rn>,#±<offset_8>*4] | 立即数偏移寻址 |

| 2 | [<Rn>,#±<offset_8>*4]! | 前索引立即数偏移寻址 |

| 3 | [<Rn>],#±<offset_8>*4 | 后索引立即数偏移寻址 |

| 4 | [<Rn>], <option> | 直接寻址 |

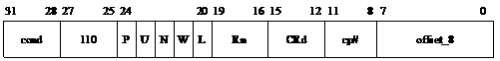

协处理器Load/Store指令的编码方式如图4.35所示。

编码格式中各标志位的含义如表4.10所示。

图4.35 协处理器Load/Store指令编码格式

表4.10 协处理器Load/Store指令编码格式各标志位含义

| 位 标 识 | 取 值 | 含 义 |

| P | P=0 | 标识使用偏移寻址还是前索引寻址(由W位决定) |

| P=1 | 标识使用后索引寻址还是直接寻址(由W位决定) | |

| U | U=0 | 从基地址中减去偏移量offset |

| U=1 | 从基地址中加上偏移量offset | |

| N | N=0 | 和具体使用的协处理器相关 |

| N=1 | ||

| W | W=0 | 指令执行结束,不改变基址寄存器的值 |

| W=1 | 访问的内存地址回写到基址寄存器 | |

| L | L=0 | Store指令 |

| L=1 | Load指令 |

1.[<Rn>,#±<offset_8>*4]

(1)编码格式

指令的编码格式如图4.36所示。

图4.36 协处理器Load/Store指令--立即数寻址

该寻址方式指定一片连续的内存地址空间。访问内存单元的第一个地址<first_addressing>等于基址寄存器<Rn>的值加上/减去指令中寄存器值的4倍。接下来的内存访问地址是前一个访问地址加4。当协处理器发出传输中止信号时,数据传送结束。

这种寻址方式的数据传输数目由协处理器决定。

| | 注意 | 这种寻址方式最多允许传输16的字。 |

(2)语法格式

<opcode>{<cond>}{L} <coproc>,<CRd>,[<Rn>,#±<offset_8>*4]

其中:

· <Rn>为基址寄存器,包含寻址操作的基地址;

· <offset_8>为8位立即数,该值的4倍为地址偏移量。

(3)操作伪代码

If ConditionPassed(cond) then

If U = = 1 then

Address = Rn + offset_8 * 4

Else /*U = = 0*/

Address = Rn – offset_8 * 4

Start_address = address

While (NotFinished(coprocessor[cp_num]))

Address = address +4

End_address = address

(4)说明

如果基址寄存器指定为程序计数器r15,则基地址为当前执行指令地址加8。

2.[<Rn>,#±<offset_8>*4]!

(1)编码格式

指令的编码格式如图4.37所示。

图4.37 协处理器Load/Store指令--前索引立即数寻址

该寻址方式指定一片连续的内存地址空间。访问内存单元的第一个地址<first_addressing>等于基址寄存器<Rn>的值加上/减去指令中寄存器值的4倍。如果指令的条件域满足,产生的<first_addressing>回写到基址寄存器Rn中。接下来的内存访问地址是前一个访问地址加4。当协处理器发出传输中止信号时,数据传送结束。

这种寻址方式的数据传输数目由协处理器决定。

| | 注意 | 这种寻址方式最多允许传输16的字。 |

(2)语法格式

<opcode>{<cond>}{L} <coproc>,<CRd>,[<Rn>,#±<offset_8>*4]!

其中:

· <Rn>为基址寄存器,包含寻址操作的基地址;

· <offset_8>为8位立即数,该值的4倍为地址偏移量;

· !设置指令编码中的W位,更新指令基地址。

(3)操作伪代码

If ConditionPassed(cond) then

- ARM指令寻址方式之: 数据处理指令的寻址方式(08-13)

- ARM汇编指令ARM寻址方式、汇编指令、伪指令(11-20)

- 单片机的指令和寻址方式(11-13)

- ARM 指令的寻址方式(11-11)

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)