基于TI最新多核DSP SoC架构解析

基础局端设备OEM厂商关注的焦点正在转变,对解决方案的功耗要求越来越高、要求可扩展的异构网络、对MIMO功能的需求以提升接受信号接受能力。对频谱效率的要求使得低时延、密集计算型处理环境越来越重要。

TI多核及媒体基础架构DSP业务部全球业务经理Ramesh Kumar表示,TI的多核SoC产品正是针对市场对上述能力的不断需求而推出的。TI了解市场正在变化,因此推出了这一多核SoC结构,期待能为设备供应商提供更快、更便利的解决方案。

TI 最近为这一系列推出了C6x新型多核 SoC 架构,运行频率高达1.2GHz、性能高达256GMACS/128GFLOPS,领先TI现有产品高达10倍以上的效率,领先市面上最先进产品5倍以上效率。目前这一架构已经推出了4核和8核系列产品,针对无线基站解决方案(包括macro/pico/femto基站)和媒体网关/网络应用。

C6x新型多核SoC架构

新的多核DSP基于40nm工艺,受益于先进的节点,新的产品将在性能、集成度、功耗上有大幅提升。除了时钟频率外,最具特点的就是集成了定点和浮点处理功能。DSP都有定点计算的功能,增加了浮点计算后,在无线基站和视频方面有很大提升。使用定点DSP,他们开发浮点算法,检测满意后,再转化成定点算法。使用这系列多核SoC,工程师不需要通过浮点转定点,可以直接进行处理,这通常也能节省3个月以上的时间。

另外,WiMAX、LTE的标准还在不断演进中,可编程DSP环境,工程师可以很快增加新的编解码器,通过软件随时更新。

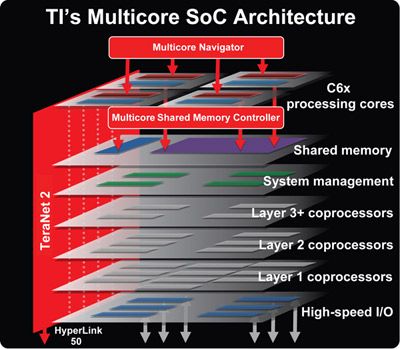

多核处理器的效能要得到发挥,对各个内核的管理和协调至关重要。如果内核无法高效互联,性能也会打折。TI花了很多精力在核间的互联上,保证高效的处理能力。 TI的SoC通过多核导航器实现内核的高效管理,它充分利用了8192任务型队列优化数据流的片上网络管理单元,采用基于主机/缓冲器描述模型使用的数据包/消息。 TeraNet 2 能够互联内核的协处理器和外设,速度达每秒2兆兆位的无阻塞主干网。除了每个内核的片上内存外,SoC还有共享的内存部分,通过共享内存控制器,无需横越TeraNet 2就可以直接访问内核。

全新的架构配合TI 多核开发工具,高效率的编译器加上最优的调试分析工具让代码更快地应用于现场,Jump Start软件还提供了GSM-EDGE、WCDMA-HSPA+、WiMAX以及LTE软件库,对3G和4G的支持也相当完善。

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)