基于FPDP和VME总线的多DSP通用并行处理系统设计方案

程、开关和软件修改对FPDP/TM、FPDP/RM进行配置,实现各个系统结构中数据实时多向传输。

3、并行处理系统板极设计

3.1 单板结构及功能描述

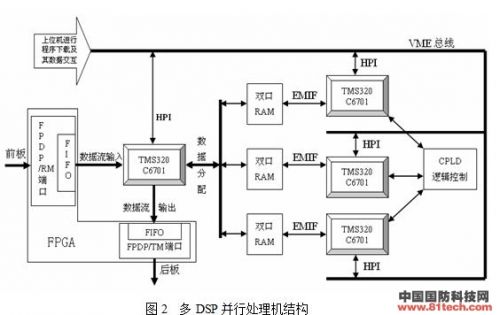

本文介绍的高速实时信号处理系统,其核心子板是多DSP并行处理机。它包括多DSP模块、VME总线模块和FPDP总线模块。DSP选用TMS320C6701芯片,它是TI公司第一代采用VelociTITM高性能超长指令字结构的高性能32位浮点型数字型号处理器,其运行时钟频率最高可达167MHz,峰值处理速度可以达到1GFLOPS和34MMACS的运算能力。

它主要包括C6701、SDRAM、FLASH、双口RAM、数据地址缓冲以及DSP附属的逻辑控制CPLD和实现两类总线协议的FPGA芯片。

多DSP并行处理系统设计的核心是实现多DSP之间的通信控制及数据交换。DSP之间的互连结构分为共享总线或共享存储器的紧耦合连接方式和拥有各自独立的数据存储器而通过通信口相连的松耦合连接方式。紧耦合连接方式限制整个系统节点数目的规模,从而降低系统的扩展性。因此,我们采用松耦合连接方式,通过双口RAM实现一主三从DSP之间的通信控制及数据交换。

VME和FPDP总线协议我们采用FPGA芯片实现。VME总线主要用于各个DSP的HPI口与上位机通讯。DSP通过VME总线采用HPI方式自动引导启动,从上位机下载程序。上位机可以通过VME总线对板上数据进行实时监控。FPDP总线连接至处理机上的主DSP,包括FPDP/TM和FPDP/RM两个功能模块。我们只需要更改和重新下载FPGA程序,便可以完成DSP处理机上的FPDP/TM和RM端口配置,以便对应整个系统结构重组。此外,用于FPDP通讯的FIFO也用FPGA实现。

处理机工作流程如下:系统上电后,4片C6701通过VME总线从上位机获取运行程序,并存入各自片内程序RAM,准备响应。前板将需要处理的数据流通过FPDP总线发送至本板FPDP/RM端口的FIFO中并且发送中断,主DSP响应中断后从FIFO中读取数据并且完成分配,分别发送至三个从DSP的双口RAM中。从DSP通过双口RAM读取数据并且进行并行处理,然后将处理完成的数据传回双口RAM。主DSP再将处理后的数据汇总并通过FPDP/TM端口发送至后板的FPDP/RM端口。如此循环,直至所有数据都处理完毕。最后主DSP将结果反馈至上位机,等待下次命令。

处理机中,每片DSP都配有一个256 K×8 bit FLASH芯片。处理机也可以脱离上位机单板工作,只需将程序提前下载到FLASH中。

3.2 单板电源设计方案

并行处理机板上需要的电源分为5V、3.3V和1.8V三类。其中5V直接来自VME机箱背板。3.3V和1.8V电源通过板上转换模块提供。由于本系统中DSP、CPLD和FPGA比较多,功耗也相对较高,其供电系统品质的好坏直接影响到整个处理机的工作稳定性。另外,并行处理机上的DSP和FPGA对其I/O电路和内核电路的供电顺序也有一定的要求。

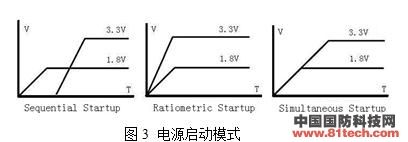

图3给出了通用器件所要求的常见的3种电源启动模式:Sequential Startup,即板上先提供1.8V电源然后再提供3.3V电源;Ratiometric Startup,即板上1.8V和3.3V电源同时以相同比率启动并且同一时刻达到稳定值;Simultaneous Startup,即板上1.8V和3.3V电源同时启动。我们在实际设计中一定要考虑到器件对供电系统的不同要求,这对处理机的稳定性具有极其重要的意义。

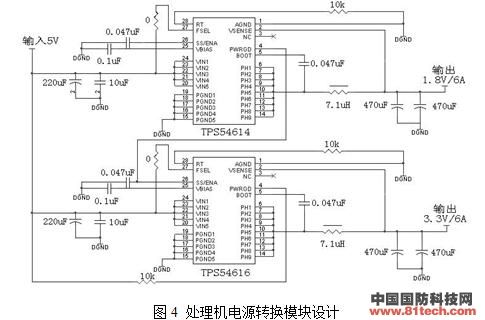

处理机上DSP和FPGA要求内核电路和I/O电路的供电采用Sequential Startup模式。整板需要5A左右的1.8V和3.3V 电源系统。由此,我们采用TI公司的TPS54614和TPS54616芯片设计了处理机的电源转换模块。它有体积小,输出电流大,性能稳定等特点。电路原理如图4所示。TPS54614采用5V输入,能够稳定提供最大电流为6A的1.8V输出,TPS54616同样采用采用5V输入,能够稳定提供最大电流为6A的3.3V输出。此电源转换模块完全满足整个信号处理机的供电量要求。

在设计中,根据TPS54610系列芯片的特性,我们将TPS54614的PWRGD连接至TPS54616的SS/ENA管脚。系统上电时,当TPS54614输出电压低于正常值的90%即1.6V时,PWRGD为低,抑制TPS54616启动,当TPS54614输出电压大于1.6V时,PWRGD变高,启动TPS54616;系统关闭时,TPS54614输出降低到1.6V时,PWRGD变低,TPS54616才开始关闭。因此保证了DSP、FPGA内核电压供电先于I/O电压,满足了系统供电采用Sequential Startup模式的要求。

3.3 电路灵活配置

3.3.1 JTAG接口菊花链设计

TMS320C6701备有基于IEEE 1149.1标准的边界扫描测试接口,从而为设计人员提供了一个实时的硬件仿真与调试环境。由于处理机是一个有4个DSP的多DSP系统,我们将DSP的JTAG接口与14 pin Hea

- 基于CPLD/FPGA/MCU的CAN-VME总线转换方案(12-16)

- 测控总线技术的现状与特点(12-11)

- VME总线产品在GE PAC系统中集成需注意的问题(12-10)

- VxWorks操作系统及实时多任务程序设计(03-27)

- 工控机VME总线(12-19)

- 简述VME总线原理及应用(09-03)