基于微处理器和射频收发芯片的近程无线数传系统设计[图]

本文介绍了一种选用高性能、低功耗的32位微处理器STM32F103和射频收发芯片nRF24L01来设计短距离无线数据传输系统的具体方法。

1 系统设计

短距离无线数传系统主要由电源管理器AMC7635、微控制器STM32F103、射频收发器nrf24l01三部分组成。下面分别介绍其关键电路。

1.1 电源电路

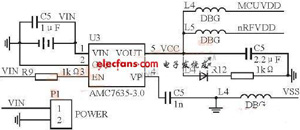

本设计的电源采用3.7V锂电池供电,然后经低压降电源管理芯片AMC7635,以产生3.0V的电压来为STM32F103和nRF24L01供电,图1所示是本系统的供电电路。

图1 系统供电电路

1.2 微控制器电路

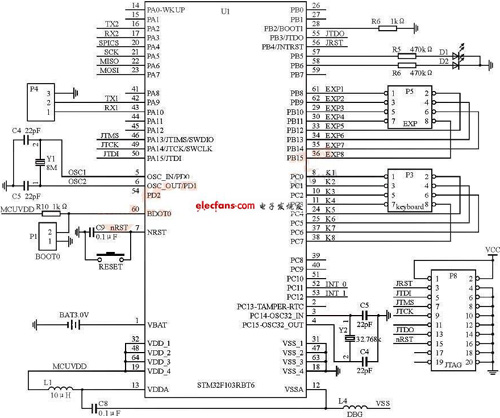

微控制器选用带ARM Cortex -M3内核的STM32F103。STM32F103控制器具有高性能、低功耗、低电压等特性,同时具有高集成度和易于开发的优势。图2所示是该系统中的微控制器电路。控制器与射频收发器nRF24L01的接口采用SPI口来实现,即图2中SPICS、MOSI、MISO和SCK四条信号线和CE和INT0两条信号线。另外,该控制器还可以扩展一路主板RS232口和8路GPIO口输出。

图2 微控制器电路

1.3 射频收发电路

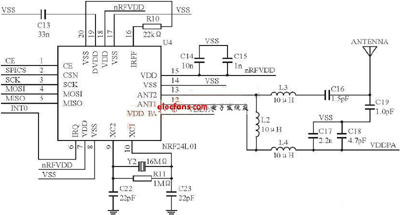

nRF24L01可工作于2.4GHz~2.5GHz ISM频段,该收发器内置频率合成器、功率放大器、晶体振荡器、调制器等功能模块,是一款集成度较高的无线收发器。nRF24L01的外部电路比较简单,而且融合了增强型ShockBurst技术,其中输出功率和通信频道可通过程序进行配置。同时,该芯片的功耗极低,在以-6dBm的功率发射时,其工作电流只有9mA;而在接收时,工作电流只有12.3mA。nRF24L01的控制电路可与STM32控制器的SPI口和GPIO口相连接。图3所示是该芯片组成的射频收发电路原理图。

图3 射频收发电路

2 系统程序设计

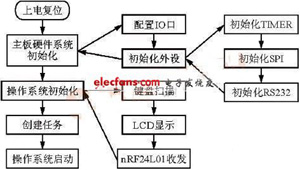

本系统可在STM32F103上移植UCOSII操作系统。系统程序主要分为主机的系统初始化程序、键盘和显示程序及射频收发器nRF24L01的控制程序三大部分。图4所示是其软件程序流程。

图4 系统程序流程图

系统程序设计的关键是UCOSII操作系统的移植和SPI口通信控制。有关操作系统的移植,芯片厂商在官网上已有范例提供,本文不再赘述。

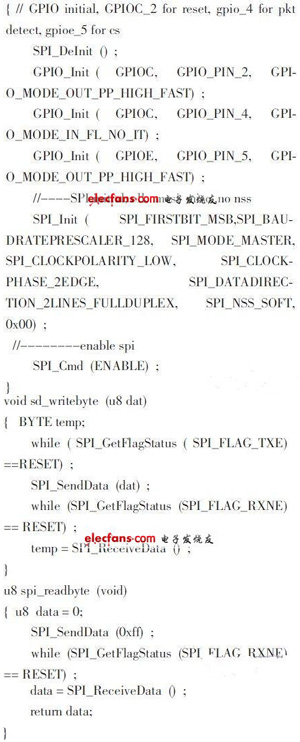

下面列出系统SPI初始化及收发函数的程序源码。

void SPI_Initial (void)

当然,也可以用GPIO口来实现SPI通信,但前提是通信速率要求不是很高。由于要通过GPIO口模拟实现SPI的突发传送协议,而且要兼顾其通用性,故其程序较为复杂。下面给出通过GPIO口实现SPI收发的一般程序:

3 结束语

经现场调试证明,本文给出的无线数传系统具有成本低,速率高,传输可靠等优点。在实际应用中,还可根据需要将nRF24LOl组成一对一、一对多、多对多的结构。

射频收发芯片 相关文章:

- 韩研发出数据流量高达10Gbps的极速无线射频收发芯片 (03-21)