TMS320VC5409和Cygnal单片机构成的移动数据处理传输系统

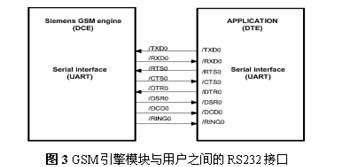

西门子的TC35系列GSM引擎模块[7]性价比较高,并且已经有国内的无线电设备入网证,TC35主要是由射频天线、内部Flash、GSM 基带处理器、匹配电源和一个40脚的Zip插座组成。其中GSM基带处理器是核心部件,它的作用相当于一个协议处理器,用来处理外部系统通过串口发送过来的AT指令。射频天线部分主要实现信号的调制与解调,实现外部射频信号与内部基带处理器之间的信号转换,匹配电源为处理器以及射频部分提供所需的电源,插座是提供给用户的应用接口。TC35的用户应用接口采用40脚的Zip插座,其中包含的引脚功能有:3.3~5.5V峰值为2A的直流电源;模拟音频输入输出接口;标准的RS232信号接口,共8个引脚;SIM卡连接引脚数为6个,符合GSM11.11标准。特别需要引起注意的是,RS232接口采用9位编码格式,其中8 个数据位,1个停止位,没有奇偶校验位,因此单片机一般采用工作方式1,支持1200-115200bps的速率(但标准的GSM网络一般只支持 9.6Kbps的速率)。

4 CPU单元

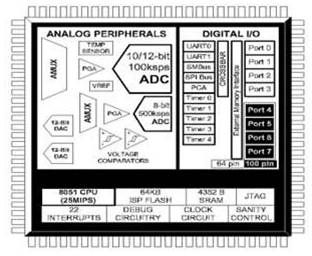

CPU单元的任务比较多,主要要完成对由DSP单元送来的信号再处理分析。 CPU单元还分别控制键盘单元、时钟单元、LCD单元、LED单元等辅助单元和GSM单元工作。对CPU单元的要求是高速和低功耗。这里选用美国 Cygnal公司的C8051F020。C8051F020单片机[8]是集成在一块芯片上的混合信号系统级单片机(图4),芯片上有8个8位数字I/O 端口,其中四个与标准的8051的端口(P0、P1、P2、P3)相同,与5V兼容。I/O端口在功能上有所增强,每个I/O端口都可独立地设置为推挽输出或开漏输出和弱上拉,这为一些低功耗系统设计提供了节省电源的手段。C8051F020单片机除了具有51系列单片机的特点外还有如下的特点:

(1) 25MPIS高速流水线式8051微控制器内核;

(2) 12位、100KSPS、8通道带可编程增益放大器的ADC,双12位可程控更新的DAC;

(3) 双模拟比较器,片内基准电源;

(4) 64KB系统内可编程FLASH存储器,4352(4096+256)片内RAM;

(5) 各自独立的SPI、SMBUS/I2C和两个UART串行接口;

(6) 5个16位通用定时器;

(7) 片内看门狗定时器、VDD监视器和温度传感器;

(8) 工作电压:2.7-3.6V,工作电流:@20MHz">10mA@20MHz。

C8051F020使用采用了流水线式结构,与标准的8051相比它的指令执行速度有极大的提高。在标准的8051中,除了MUL和div所有的指令都需要12或24个系统时钟周期,最大的时钟频率12-24MHZ。相比较而言,C8051F020内核70%的指令执行时间为1或2个系统时钟周期,只有4 条指令的执行 时间超过4个系统时钟周期。C8051F020的MCU 在CIP-51内核的内部和外部有几项关键性的改进,提高了整体性能,更易于在实际应用中使用。扩展的中断系统为CIP-51提供22个中断源,而标准的8051只有7个中断源。C8051F020允许大量的模拟和数字外设中断微控制器。由中断驱动的系统需要较少的CPU干预,从而极大地提高系统的执行速度。特别是在多任务实时系统中,这些增加的中断源非常有用。MCU内部有一个能独立工作的时钟发生器。另外,MCU可以关闭单个或全部外设以节省功耗。由于C8051F020单片机自身带有64K+128B的 FLASH 程序存储器,故不需再扩展程序存储器。

图4 C8051F020单片机

C8051F020的MCU具有4KB的RAM可映射在片内,也可映射在64KB外部数据存储器地址空间,还可同时映射到片内和片外三种方式。对于后两种存储器工作模式需通过外部存储器接口使用MOVX和DPTR或MOVX和R0(R1)指令访问外部数据存储器和存储器映像的I/O设备。但是对于高8位地址必须由外部存储器接口寄存器(EMI0CN)提供。而EMIF控制寄存器可将外部数据存储器接口映射到低端口(P0-P3)或高端口(P4-P7),以及配置为复用模式或非复用模式等。

外部存储器接口(EMI)映射为低端口(P0~3)即PRTSEL位(EMIOCH.5)置为0,此时如果EMIFLE位(XBR2.5)被设置为逻辑1,那么数字交*开关将不分配外部设备给 P0.7(/WR),P0.6(/RD),P0.5(ALE)(如果EMI设置为复用模式);如果EMIFLE位设为0,那么P0.7、P0.6、 P0.5的功能将由交*开关或端口锁存器来决定。外部存储器接口只在执行片外MOVX指令期间使用相关的端口引脚,一旦MOVX指令执行完毕,端口锁存器或交*开关又重新恢复对端口引脚的控制(端口3、2、1、0)。对于外部存储器接口的配置只有扩展外部存储器或具有存储器映像的I/O部件时,才配置 EMIF。

本数据处理传输系统使用512k*8bit的SRAM作为外部数据存储器,使用高端口、复用模式(即P7端口数据D0-D7和地址A0-A7复用,P6端口输出地址A8-A15)、片外存储器方式(不使用片内存储器)。DCM8512是512k*8bit自带掉电保护的 SRAM,用于存放数据和VC5409用户程序,需19条地址线(A0-A18),而C8051F020外部数据存储器只支持64k Byte(A0-A15),故使用P5端口来扩充地址线(A16-A20)。

C8051F020最突出的优点之一就是使用交*开关网络。交*开关网络改进了可以控制片内数字资源与外部I/O引脚相连的。通过设置交*开关控制寄存器,将片内的数字资源如计数器/定时器、串行总线、硬件中断、 ADC转换启动输入、比较器输出以及微控制器内部其他数字资源配置为端口I/O引脚,这就允许用户根据自己的特定应用将通用I/O端口与所需要数字资源相结合。

CPU单元工作原理(见图5)。C8051F020的工作频率为11.0592MHz。模拟信号连接至C8051F020的 AIN0.0- AIN0.7脚,进行12位A/D转换。由C8051F020中的时钟单元产生可以变动的抽样频率。CPU单元通过HPI总线将A/D转换后的心电信号送到DSP单元进行运算,运算的结果再通过HPI总线送入CPU单元。HPI总线内包括数据线D0-D7、地址线A0-A3、DSP片选线DSP- addr、读写线WR,RD、DSP复位线及中断线INT0组成。地址线A0-A3选择DSP的HPI寄存器;数据线D0-D7用于C8051F020和 DSP交换数据;当C8051F020向DSP写数据时,将在DSP内部产生中断,该中断将DSP从IDLE状态中唤醒,中断服务程序还将从DSP特定地址的内部存储器中读CPU写的数据;当DSP向C8051F020写数据时,DSP置中断线INT0=0,C8051F020的INT0中断服务程序将从 DSP的HPI数据寄存器读数据。

TMS320VC5409 Cygnal单片机 移动数据处理 相关文章:

- 基于闪烁存储器的TMS320VC5409 DSP并行引导装载方法(05-23)

- 基于闪存TMS320VC5409DSP并行引导装载方法(07-05)

- 基于DSP的IP电话设计 (10-08)

- TMS320VC5409与Cygnal构成的移动数据处理传输系统(01-21)

- 基于DSP的IP电话设计 (1)(11-08)