80C32E单片机与TLV2548串行A/D的接口设计

O 引言

TLV2548是TI公司生产的12位、多通道、小尺寸、低功耗、高速串行A/D转换芯片,它有一个专与DSP连接的帧同步(FS)信号,故可广泛用于DSP高速数据采集系统中。

MCS-51系列单片机历经了多年的发展,其应用技术已十分稳定可靠。TLV2548尺寸小、接口简单。且这两种芯片都有过上天飞行的经历,因此,可以适用低成本、控制简单、数据处理量不大、可靠性要求较高的航天产品中。

为此,本文将介绍80C32E单片机与TLV2548的接口电路及其控制程序的设计方法。

1 接口电路设计

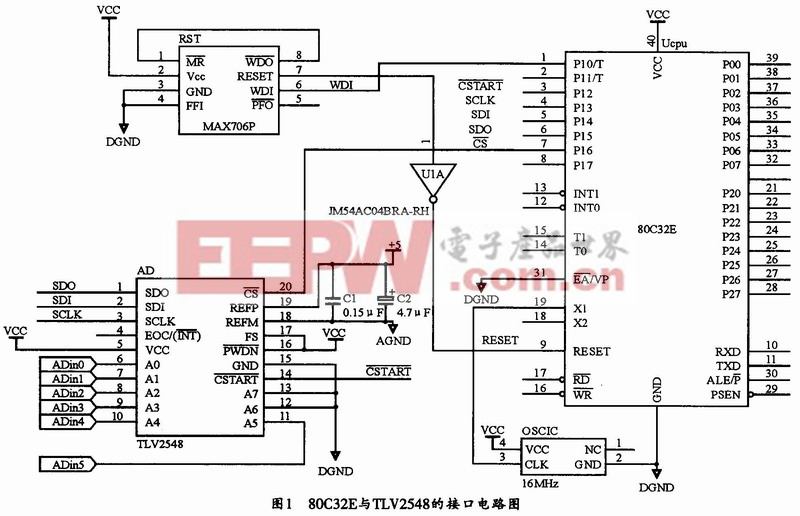

80C32E与TLV2548的接口电路如图1所示。

TLV2548提供了一个SPI串口。80C32E则采用通用I/O口(P1),并通过软件编程产生SPI串行接口信号,从而实现对TLV2548的控制与数据的读写。

TLV2548有5个控制引脚 、FS、SCLK、

、FS、SCLK、![]() 和

和 。其中FS为DSP专用帧同步信号,在微控制器控制方式时,可将其接高电平;

。其中FS为DSP专用帧同步信号,在微控制器控制方式时,可将其接高电平; 为低电平时,片内的模拟电路与参考电路进入节电状态。由于本文不使用节电方式,因此将其接高电平。另外,

为低电平时,片内的模拟电路与参考电路进入节电状态。由于本文不使用节电方式,因此将其接高电平。另外, 引脚为转换结束及向处理器请求中断信号,

引脚为转换结束及向处理器请求中断信号,![]() 的下降沿表示转换后的数据可以输出,本电路中,此信号没有连接,因为TLV2548的转换速度很快(3.6μs),而单片机中断与查寻方式不能提高时间效率,故采用软件延时等待转换结束,这样编程比较简单,同时也可节省80C32E的硬件资源。数据线SDI与SDO为80C32E与TLV2548之间的数据传输线。

的下降沿表示转换后的数据可以输出,本电路中,此信号没有连接,因为TLV2548的转换速度很快(3.6μs),而单片机中断与查寻方式不能提高时间效率,故采用软件延时等待转换结束,这样编程比较简单,同时也可节省80C32E的硬件资源。数据线SDI与SDO为80C32E与TLV2548之间的数据传输线。

TLV2548有单次(00)、重复(01)、扫描(10)及重复扫描(11)模式四种转换模式,各模式的用法略有区别;有普通与扩展两种采样方式。扩展采样方式的优点在于A/D的采样与转换时间不受时钟信号SCLK的限制,其采样、转换由 电平控制。时间短、速度快。本文选用11重复扫描模式与扩展采样方式,来对TLV2548中的6个通道(A0~A5)进行转换。

电平控制。时间短、速度快。本文选用11重复扫描模式与扩展采样方式,来对TLV2548中的6个通道(A0~A5)进行转换。

图l中的MAX706为看门狗复位电路,OSCIC为16 MHz晶振。

80C32E与TLV2548之间的数据与命令是以16位二进制形式传输的。其命令格式为:高4位命令+低12配置字。配置寄存器(CFR)读出格式为:高4位忽略+低12位寄存器内容。A/D转换值(FIFO)读出格式为:高12位转换值+低4位忽略。

80C32E接口控制程序的任务是产生A/D采样和转换信号,以及SPI串口时序,同时完成TLV2548的转换启动、转换方式的设定及转换结果值的读取。其程序流程如图2所示。

下面结合图1和图2对TLV2548的接口控制程序进行介绍。

首先是初始化,即上电后由80C32E对TLV2548进行配置。配置时,首先置SCLK(P1.3)为低电平。其次,置低![]() (P1.6),使

(P1.6),使![]() 信号产生一个下降沿。此时由于FS为高电平。这样,当

信号产生一个下降沿。此时由于FS为高电平。这样,当![]() 的下降沿来临时,TLV2548默认为微控制器(μP)系统,它将复位内部计数器并使能SDI与SD-O。最后,80C32E向TLV2548(CFR)写入命令字A000H,从而完成对TLV2548的初始化,其程序代码为:

的下降沿来临时,TLV2548默认为微控制器(μP)系统,它将复位内部计数器并使能SDI与SD-O。最后,80C32E向TLV2548(CFR)写入命令字A000H,从而完成对TLV2548的初始化,其程序代码为:

配置时。可选用TLV2548外部参考电压和内部振荡器,并选mode 11重复扫描模式,扫描序列为0一l一2—3—4—5,扫描序列长度3/4。其具体代码为:

3 实验结果

当80C32成功执行初始化配置后,通过清、置 可向TLV2548发送6个脉冲,以启动A/D采样和转换。A/D输出

可向TLV2548发送6个脉冲,以启动A/D采样和转换。A/D输出![]() 下降沿表示转换完成,其结果数据可以输出。随后的

下降沿表示转换完成,其结果数据可以输出。随后的![]() 下降沿将使

下降沿将使![]() 信号变为高电平,同时选中TLV2548并使SDI与SDO有效。最后,由80C32发出串行时钟信号SCLK(P1.3)并通过SDI、SDO移出命令和读入数据。图3所示为运行上述程序后的TLV2548控制时序图。

信号变为高电平,同时选中TLV2548并使SDI与SDO有效。最后,由80C32发出串行时钟信号SCLK(P1.3)并通过SDI、SDO移出命令和读入数据。图3所示为运行上述程序后的TLV2548控制时序图。

目前,该方案已应用于某航天任务中,实践证明,本系统性能良好,并已通过电性、鉴定、正样等产品验收。鉴于单片机的兼容性,本文所介绍的接口电路与程序也可应用于其它型号的MCS-51系列单片机中。

接口 设计 串行 TLV2548 单片机 80C32E 相关文章:

- μC/OS-II下通用驱动框架的设计与实现(07-23)

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)

- DSP和Flash接口技术的实现(08-15)

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)