基于TMS320DM642的CCD图像采集系统设计

数字视频信息,选用1片FLASH存储器用于固化程序和一些掉电后仍需保存的用户数据。SDRAM芯片和FLASH芯片均通过TMS320DM642的EMIF口实现无缝连接[3]。TMS320DM642的EMIF有4个独立的可设定地址的区域,称为芯片使能空间(CE0~CE3),当FLASH和FPGA映射到CE1时,SDRAM占据CE0,CE3的一部分被配置给OSD功能的同步操作和扩展的FPGA中的其他同步寄存器操作。本系统合并形成了一个64 bit长的外部存储器端口,将地址空间分割成了4个芯片使能区,允许对地址空间进行8 bit、16 bit、32 bit和64 bit的同步或不同步的存取,并且使用了芯片使能区CE0、CE1和CE3。CE0被发送给64 bit的SDRAM总线,CE1被8 bit的FLASH和FPGA功能使用,CE3被设置成同步功能。

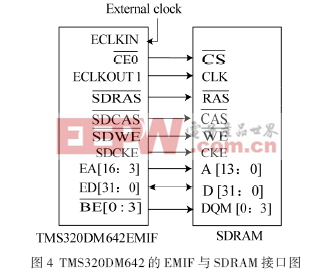

2.3.1 SDRAM存储器

本系统采用MT48LC4M32B2[4]来构成SDRAM存储器,大小为1 M×32 bit×4 banks, 在CE0空间连接了64 bit的SDRAM总线。总线由外部PLL驱动设备控制,在133MHz的最佳运行状态下运行,SDRAM的刷新由TMS320DM642自动控制。TMS320DM642的EMIF与SDRAM接口图如图4所示。

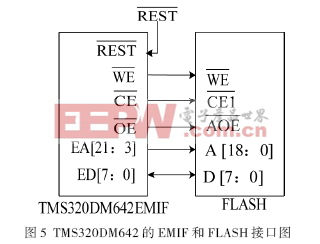

2.3.2 FLASH存储器

本系统扩展4 M的FLASH,映射在CE1空间的低位。FLASH寄存器选用4 M×8 bit的AM29LV033C。FLASH寄存器主要用来导入装载和存储FPGA的配置信息。CE1空间被配置成8 bit,FLASH寄存器也是8bit。由于CE1的可利用地址空间小于FLASH的空间,所以利用FPGA可产生3个扩展页。这些扩展的线形地址通过FPGA的FLASH基础寄存器进行定义,复位后的默认值是000。TMS320DM642的EMIF和FLASH的接口图如图5所示。

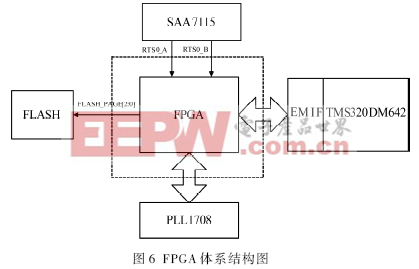

2.4 OSD FPGA模块

FPGA负责完成所有芯片的接口和控制,其中包括SAA7115与I2C总线的接口、复位控制信号以及与TMS320DM642的EMIF接口和外设接口等,其体系结构图如图6所示。本系统的OSD FPGA功能模块的芯片型号为Xilinx XC2S300E-6PQ208C[5],主要用来完成以下工作:

(1)通过寄存器使用TMS320DM642外部存储器接口(EMIF);

(2)通过可编译寄存器使用TMS320DM642的EMIF接口控制GPIO;

(3)产生EMIF缓冲控制信号(DIR和OE);

(4)提供对于PLL1708的连续控制接口;

(5)为FLASH产生3页bit空间;

(6)使用SAA7115的同步信号。

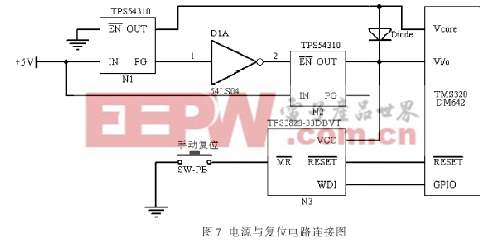

2.5 电源和复位模块

该系统通过单+5 V供电,在板子内部转换为+1.4 V和+3.3 V,为各器件供电。+3.3 V为TMS320DM642的I/O口、解码器及其他芯片的电源,+1.4 V为TMS320DM642 CPU内核电源。TMS320DM642内核电压+1.4 V,外设I/O电压+3.3 V,降低内核电压主要是降低功耗,外部接口引脚采用+3.3 V电压,便于直接与外部器件接口。由于是2种不同的电压,所以要考虑供电系统的配合问题。在加电过程中,保证CPU内核电源先加电,最晚也应当与外设I/O电源同时加电。关闭电源时,先关闭I/O电源,再关闭内核电源。如果内核加电晚于I/O,则会发生内部总线竞争,从而产生不可预定的结果。因此,选用电源芯片TPS54310[6]获得上述2种电压,并利用其电源输出有效引脚PG和允许电压输人引脚EN保证TMS320DM642的内核和I/O上电掉电顺序。

为防止系统程序进入死循环或因电压波动而产生异常,本系统用看门狗芯片来控制系统复位。这里采用TI的TPS3823-33DBVT[7]看门狗芯片,它由+3.3 V电源供电,能对电源电压进行监控,当电源电压降至2.93 V以下时触发复位信号,使整个系统进入复位状态,直至电源电压复原,复位信号的最小长度为200 ms。同时,还含有一看门狗计时器,用来监测来自处理器芯片的跳变沿触发信号,如果1.6 s内未接收到触发信号,它同样让系统进入复位状态并持续200 ms,这样可在系统程序进入死循环后重新启动系统。TMS320DM642电源与复位电路的连接图如图7所示。

3 抗干扰设计

由于高频脉冲噪声对本系统危害最大,为了提高系统的抗干扰性能,可采取以下措施:

(1)优化PCB印制板的设计。在本系统中应当:

①采用短而宽的导线来抑制干扰。时钟引线、总线驱动器的信号线常有大的瞬变电流,其印制导线要尽可能短。对于分立元件电路,印制导线宽度在1.5 mm左右即可满足要求;对于集成电路,印制导线宽度在0.5 mm~1.0 mm之间选择;

②传输多种电平信号时,尽量把前、后沿时间相近的电平信号划为一组传输;在双面印制板的背面布置较大面积的地线区域,可对部件产生的高频脉冲噪声起到吸收和屏蔽的作用;分开模拟和数字电源层;

(2)增加总线的抗干扰能力。采用三态门形式的总线结构,并给总线接上拉电阻,使总线在瞬间处于稳定的高电平而避免总线出现悬空状态。

本文面向实时图像采集和处理,采用模块化设计思想,以TMS320DM642、SAA7115、OSD FPGA等实现了视频图像采集和处理系

系统 设计 采集 图像 TMS320DM642 CCD 基于 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)