SPI4.2总线应用和调试经验谈

SPI4.2总线协议定义了一个叫“日历”的数据结构CALENDAR[i](i=1,…,CALENDAR_LEN)。CALENDAR_LEN(日历长度)参数规定了逻辑端口(或称为虚拟通道)的数目,该数值不能小于实际的逻辑端口数目。例如,如果SPI4.2总线用于10 Gb/s以太网口,那么日历长度是1(即CALENDAR_LEN = 1);如果SPI4.2总线用于10个1 Gb/s以太网口,那么日历长度是10(CALENDAR_LEN = 10),CALENDAR[i] = 1,2,…,10,代表了10个以太网端口。CALENDAR[i]中承载的数据被周而复始地依次传输,重复次数是CALENDAR_M次。图3为日历长度和重复次数都是4的数据传输示意图。SPI4.2总线被初始化时,必须确保接口两端的CALENDAR_LEN和CALENDAR_M分别相等。从这个角度看,SPI4.2是一种时分复用的总线:总带宽是固定的,“日历”数据结构决定了带宽和逻辑端口的分配。

当SPI4.2正常工作时,数据和状态链路会不定期地发送训练序列。在数据链路,训练序列至少应该在DATA_MAX_T个时钟周期内发送一次。在状态链路,训练序列至少应该在FIFO_MAX_T个时钟周期内发送一次。设置DATA_MAX_T或FIFO_MAX_T为0将取消各自链路的训练序列,一般情况下不推荐这种设置。

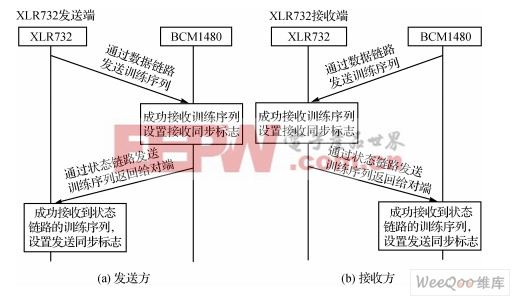

图4以XLR732为参照描述了SPI4.2总线的收发同步过程。启动之后,在发送方向,发送模块(TX)通过数据链路发送连续的训练序列,对端的接收模块成功收到训练序列后,会设置本端的接收同步标志;然后通过状态链路发送训练序列给对端,一旦发送模块成功接收到训练序列后,就设置本端的发送同步标志。

在接收方,接收模块(RX)在数据链路成功接收到对端发送的训练序列后,会设置本端的接收同步标志;然后通过状态链路发送训练序列,一旦发送模块成功接收到训练序列后,就设置本端的发送同步标志。在同步过程中,训练序列由指定的连续的DIP4码字组成。发送模块必须连续发送训练序列,直到本端的状态链路收到有效信息。同时,接收模块忽视所有接收到的数据,直到观察到训练序列,获得数据同步。一旦数据链路同步之后, FIFO队列状态信息就开始传送。

如果发送方接收到有效的状态信息,它就可以开始进行数据突发传输。如果在工作过程中,由于某些原因(例如一端器件掉电或重启)导致总线失步,那么为了再次获得同步,双方需要按照上述过程发送连续的训练序列,直到建立同步为止。

表1 SPI4.2初始化基本参数

图3 日历长度和重复次数都为4的数据传输示意图

图4 收发同步过程示意图

3 SPI4.2总线接口的调试

SPI4.2总线接口的调试包括两个重要步骤:链路的同步和数据的正常收发。

在调试链路同步时,首先必须查看总线两端的初始化参数配置。因为SPI4.2 总线协议是一个对等端数据传输协议,所以大部分参数需要双方的匹配和协商,特别是接收方和发送方的CALENDAR_LEN和CALENDAR_M参数。

如何查看同步呢?芯片通常会提供一个状态寄存器来反映总线的同步。“接收同步标志”只能说明在数据链路上成功接收到对端的训练序列,但不能保证接收的状态链路是正常的,如果需要确认可查看对端的“发送同步标志”。在收发双向通道应用中,只有两端的“接收同步标志”和“发送同步标志”都置位了,总线才算同步。此时,可以确认总线两端的物理连接是正确的,握手成功。

如果不能同步,就必须检查两端的“接收同步标志”和“发送同步标志”,判断是哪一端出了问题。检查是否有DIP4和DIP2错误,如果有此类错误,说明链路上信号质量可能不佳,可以用示波器测量信号波形。如果信号质量确实不好,可以通过提高信号驱动能力或者调整硬件匹配阻抗来优化。

如果两端的接收和发送都没有同步,就必须测量芯片的电压、工作频率、重启等信号。如果两端的“接收同步标志”和“发送同步标志”都已经置位,说明双方的接收和发送都同步,可以正常收发数据了。在大流量数据传输过程中,最相关的是FIFO队列的参数配置,配置不当会导致错包或丢包。以NetLogic公司的XLR732网络处理器为例[2],SPI4.2总线的发送模块的所有逻辑端口共享一个FIFO队列,宽度为16字节,长度为128;接收模块的所有逻辑端口共享一个FIFO队列,宽度为16字节,长度为512。每个逻辑端口所占用的队列地址和大小都可以通过寄存器配置。

假如某个端口接收端队列的长度是48,MaxBurst1是12,MaxBurst2是8。那么当该模块接收数据时,如果由于某些原因(例如软件来不及处理),接收队列只剩下12个空位,也就是接收队列已经有48-12=36个空位被占用时,它将通过状态链路向对端发送“饿”的状态信号(反压信号)。对端收到该信号后实施流控策略,根据本端

- 基于RS-232总线的测控系统开发(12-13)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)