级联两个十进制计数器实现19阶连续计数器

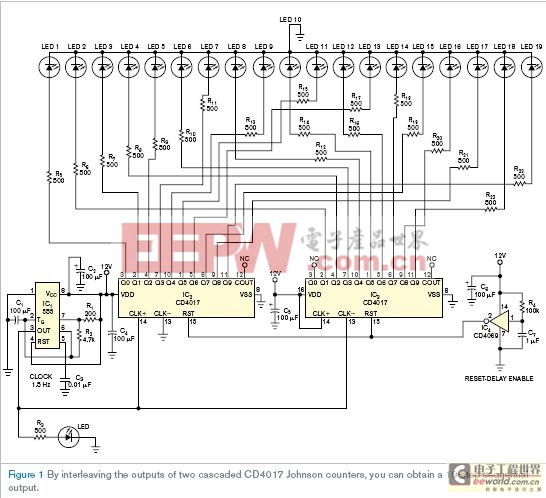

交叉一对Johnson计数器的输出,获得19阶连续计数器。

本设计方案提出一个用极少器件级联两个或更多Johnson计数器的实用方法。CD4017 Johnson十进制计数器应用于从声效到LED显示的简单电路中。计数器输出通常为低,只在各自解码时间内变高。每个解码输出在一个全时钟周期内保持高电平。直流供电电压范围从大约3V到18V。每个输出管脚(Q0到Q9)的直流电流消耗为10mA。电路通过了12V直流0到150°F温区内的无异常测试。

图1电路只使用四个IC,组成19阶连续计数器。由于供电后每个CD4017计数器的输出Q0都工作,所以不能在没有增加硬件的情况下得到20输出。因此,电路不能够使用IC3的Q0输出,而只能使用20个输出的19个。

初看上去,也许会考虑使用动作管脚(管脚12)从一个计数器接到第二个计数器的时钟输入管脚(管脚14),简单的级联两个计数器。但是这个结构一旦第一个计数器达到10,就开始重新计数,不能提供1到20的连续计数。这样的结构为0到99计数器,因为第一个IC计数器中每10个计数引发第二个计数器的一个计数。

通过连接两个计数器

没有延时时间,每个计数器上电后,计数输出是随机的,这样若干LED也许是亮的。电路用IC1的555定时器产生1.5Hz方波作为时钟。可以通过改变由R1、R2和C1组成的RC时间常数来改变频率。务必牢记,为获得占空比50%的输出,使R2远大于R1。IC2的管脚14为正边沿时钟触发。IC3的管脚13为负边沿时钟触发。因此,当时钟变为高电平时,IC2产生一个计数输出。当时钟变为低电平时,IC3产生一个计数输出。通过交叉输出,获得1到19的连续计数。因为每个时钟周期都是高低电平状态,第一个时钟脉冲后,两个LED通常是亮的——也就是说,LED1,LED1和2,LED2和3,LED3和4,等等。

- 基于单片机的智能计步器设计(09-20)

- 调整单片机时钟精度的解决方案(10-04)

- verilog HDL基础之:实例3 数字跑表(06-05)

- 基于FPGA的PWM计数器改进设计(06-05)

- 采用Verilog的数字跑表设计及实验(06-05)

- 基于Microblaze软核FSL总线的门光子计数器设计与实现(06-05)