PCF2111CT字符液晶驱动模块

PCF2111CT模块的主要特点有:(1)工作电压要求范围大,DC2.25V—6.0V;低功耗,最大功耗100mW;(2)内置振荡电路,无需外接振荡器,只要在振荡器输入端与电源跨接一个电容,与地跨接一个电阻即可,使用设计方便;(3)数据串行连续输入,与外围电路特别是单片机连接时,只需3根线,可以节约单片机的I/O口;(4)具有加电自动复位功能;(5)具有液晶底板背光驱动功能。

一、引脚功能介绍

PCF21XXC系列产品有多种封装形式,PCF2111CT采用的是VSO40封装,引脚排列如图1所示。

各引脚功能描述如下:

1脚,CLB:外部同步时钟输入;

2脚,VDD:电源电压正极,DC2.25—6.0V;

3脚,OSC:振荡器输入,外接一个电阻和电容;

4脚,VSS:电源地;

5"36脚,S1"S32:LCD驱动输出;

37、38脚,BP1和BP2:背光驱动;

39脚,DATA:串行数据输入线;

40脚,DLEN: 数据输入允许(DLEN=1,允许输入;DLEN=0,禁止输入)。

二、内部结构与工作原理

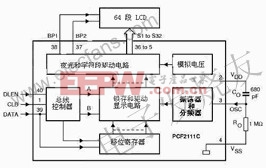

PCF2111CT内部结构如图2所示。

内部电路主要包括振荡分频器、移位寄存器、锁存和驱动显示电路、总线控制电路、模拟电压产生电路、字符段驱动电路。该模块内置集成了振荡电路,所以在引脚3与引脚2(电源)之间跨接一个680Pf电容,与4脚(地)之间跨接一个1M欧姆的电阻电路就可以起振,经过分频器送给锁存和驱动电路工作脉冲。外部输入信号CLB、DLEN、DATA送到总线控制器。DATA信号的另一路送至串行入/并行出移位寄存器,总线控制器负责移位寄存器的清零;总线控制器还控制锁存驱动电路对移位寄存器的并行读取(B)和输出驱动(A)。字符段驱动电路收到信号后转换电平,提高驱动负载能力,送至LCD显示。

三、工作时序

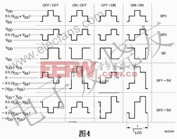

如图3所示:DLEN数据输入控制信号高电平有效;当DLEN高电平时,同步时钟CLB输入起始脉冲,同时数据DATA发送低电平起始位,在每次同步时钟上升沿到来时,DATA先后输入32位数据S1"S32;当同步时钟CLB第34个脉冲到来时,数据线输入第33个脉冲(结束位),当结束位高电平到来时启动背光控制BP1,低电平时启动BP2。随后同步时钟CLB输入第35个脉冲,通知总线控制器一组数据(32位)输入完成。综合上述,每组数据的输入需要35个同步时钟,33个数据位,数据复用率1:2。当在数据输入过程中,写入不足32位时,DLEN变为低电平,立即封锁输入端口,电路重新接收数据。

背光和字符段驱动时序如图4:

四、应用电路

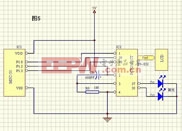

在PCF2111CT应用中,与单片机控制电路的连接非常简单,仅仅需要三线。这里以MCS-51单片机为例,如图5所示:4脚接地,2脚接5V,1脚、39脚、40脚分别接单片机的P1.0 、P1.2、P1.3脚,37、38脚接发光二极管,用于液晶的背光显示。单片机的P1.0、P1.2、P1.3三脚分别充当同步写入时钟CLB、数据输入DATA、输入控制DLEN的功能。初始化单片机时置P1.3为低电平,写入数据时,置P1.3高电平。

汇编语言显示子程序(仅作参考):

初始化单片机时定义三个引脚

CLB BIT P1.0 ;定义P1.0同步输入时钟CLB

DATA BIT P1.2 ;定义P1.2为数据输入DATA

DLEN BIT P1.3 ;定义P1.3为输入控制DLEN

…………………….. ;单片机主程序

显示子程序

DISPLAY:

CLR CLB

MOV DPTR,#DISPDAT ;查表

MOV R5,#00H ;(R5可做入口参数,用于查表)

MOV R6,#04H

SETB DLEN ;输入允许

SETB CLB

CPL CLB ;起始脉冲

n

bsp;CLR DATA ;发送起始位

MOV A,R5

LOOP2:

MOVC A,@A+DPTR ;读数据

MOV R7,#08H

LOOP1:

RRC A ;进位右移

SETB CLB ;上升沿

MOV DATA,C ;传送SX

CPL CLB

DJNZ R7,LOOP1 ;8位传送是否结束,不是则循环

INC R5 ;准备读下八位

DJNZ R6,LOOP2 ;32为是否传送完毕

SETB CLB ;第34个脉冲

SETB DATA ;结束位,驱动BP1

CPL CLB

CPL DATA ;驱动BP2

CLR DLEN ;输入禁止

SETB DATA ;置高电平位,准备下次输入的起始位

SETB CLB

CPL CLB ;第35个脉冲,通知总线控制器传送完毕

RET

………….

DISPDAT:

DB 89H, B5H, 0F2H, 31H

DB E8H…………….

………………………

END

- 基于ARM9&Linux的液晶驱动终端设计(04-30)

- 32 x 8段液晶驱动HT1622 程序(11-23)

- T6963c液晶驱动芯片(08-04)

- MSP430F1121与液晶驱动芯片PCF8576的连接程序(06-27)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)