一种基于MPC8260和FPGA的DMA接口设计与实现

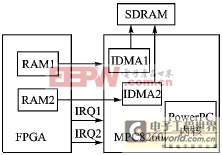

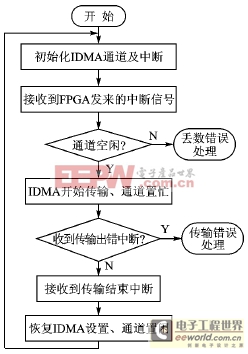

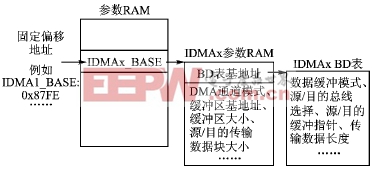

次传输的数据长度比较长,内核写一个寄存器的额外开销就完全可以忽略不计。同时,由于内部命令触发方式不需要握手信号,不需要频繁地每几个字节就竞争一次总线控制权,所以这种方式的传输效率更高、传输速度更快。内部命令触发方式是以空间换时间——用前端大的缓冲区来换取传输速度的提升。 考虑到主控板上软硬件系统的瓶颈都在于总线带宽,而存储资源相对比较丰富,所以选择CP命令控制的IDMA传输作为数据流从FPGA到SDRAM的传输方式。 2 DMA传输方案设计 FPGA和MPC8260间的数据传输接口设计如图3所示。图中左侧FPGA,通过16位数据线、10位地址线、2根中断请求线和一些读写控制信号线连接到右侧的MPC8260。MPC8260通过64位数据线与本地内存SDRAM相连。 图3 IDMA传输设计框图 FPGA内部分配有两个大的存储空间,用于轮流缓冲从数据源接收到的数据。任何一个缓冲区收满后,继续接收的数据保存到下一个缓冲区,同时以中断的方式触发MPC8260启动相应的IDMA通道把数据传到SDRAM中。IDMA控制、数据同步和错误处理都由MPC8260完成,FPGA只负责收发数据和触发中断。下面分别介绍二者的程序设计。 2.1 MPC8260程序设计 MPC8260内部的程序处理流程如图4所示。MPC8260预先初始化两个IDMA通道:通道的源地址和传输数据长度等信息与FPGA中的缓冲区一一对应。当收到FPGA的中断信号之后,如果此时对应的IDMA通道空闲,则在中断处理程序中发出CP命令开始接收数据,同时将对应的IDMA通道置忙状态;否则,在FPGA中可能发生了未读取的数据被覆盖的情况,MPC8260进入错误处理程序。在数据传输结束时由DMA控制器发送CPM内部中断到内核,在中断处理程序中一方面要恢复IDMA通道的参数设置,另一方面要把该IDMA通道置闲状态等待下一次传输的开始。 MPC8260程序的核心部分是IDMA通道设置和中断处理。 图4 MPC8260传输处理流程 2.1.1 IDMA通道设置 与一般的DMA通道设置一样,IDMA通道设置的主要参数包括:源地址、目的地址和传输数据长度。除此之外,MPC8260的 IDMA通道设置还包括通道模式、缓冲区和中断配置等,所涉及的寄存器比较多,配置比较复杂。IDMA通道设置的逻辑结构如图5所示。 图5 IDMA通道设置的逻辑结构框图 BD(Buffer Descriptors)表是用于指定传输方式、源/目的地址和数据长度等基本信息的数据结构。BD表的基地址由参数RAM中IBASE寄存器的值指定。IDMAx_BASE寄存器的地址是固定的,如IDMA1_BASE在偏移RAM基地址0x87FE的位置。CP就是通过IDMAx_BASE寄存器找到IDMA参数RAM,再通过IBASE找到BD表的顺序初始化IDMA通道的。具体的寄存器配置可以参考文献[1]第19章的IDMA编程示例。 为了提高通道的传输速率,系统中IDMA通道初始化应该注意以下几点: ① 需要在SIU中为FPGA配置UPM模式控制MPC8260和FPGA之间的突发读写。不要使用通用目的片选机(GeneralPurpose Chipselect Machine,GPCM)模式。因为MPC8260内存控制的GPCM模式不支持突发传输,IDMA工作在GPCM模式下一方不论传输数据的长度是否满足突发的要求,都只能以普通的单次读写进行。 ② 把FPGA当作存储器操作,IDMA工作在内存到内存的双地址模式下,缓冲区设为最大的2 KB。 ③ BD表的配置应该与FPGA中的缓冲区一一对应。BD表结构中的CM(Continuous Mode)位应该设置为缓冲链模式,在每一个BD表传输完之后,清BD表的有效位;同时,CP根据下一个BD表的值自动装载IDMA寄存器进行后面的传输。 IDMA通道初始化以后等待CP发出START_IDMA命令开始传输。在最后一个BD表传输结束时触发中断信号通知PowerPC内核本次传输过程的完成。传输过程中会发生改变的通道设置寄存器包括IDMA BD表指针、源地址、目的地址和BD表有效位等,所以在BD表传输结束的中断处理程序中需要恢复这些寄存器为下一次传输作准备。 2.1.2 中断处理 中断处理是与计算机专业有关的术语。引起中断的事件称为中断源。中断源向CPU提出处理的请求称为中断请求。发生中断时被打断程序的暂停点成为断点。CPU暂停现行程序而转为响应中断请求的过程称为中断响应。处理中断源的程序称为中断处理程序。CPU执行有关的中断处理程序称为中断处理。 与一般中断处理过程的区别在于:MPC8260中断处理控制器采用分级结构来扩展中断信号总数。CPM内的中断就是二级中断,需要通过CPM中断控制器和SIU中断控制器两级中断控制。本设计中用来通知内核本次传输过程结束的中断是CPM内最后一个BD表传送结束的信号BC(BD Completed)。BC信号和命令结束等几个信号一起通过SIU中断挂起寄存器中的IDMA位向内核发出中断信号。

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)