软件无线电平台可重配置接口的实现

传输。

1.3 FPGA的逻辑设计

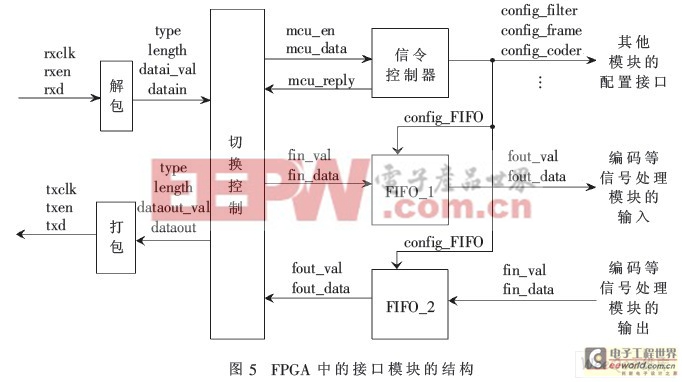

在接口电路中传输的是装载了用户数据/信令的网络包,在接口两端(即上位机和FPGA)都需要有相应的接口模块来对网络包进行解析和封装。本文重点介绍FPGA端的接口模块,如图5所示,由6个子模块组成:解包、打包、信令/数据切换控制、信令控制器以及FIFO。其中,解包是从MII口收取网络包,根据网络包的格式取出其中的信令/数据;打包是将信令/数据按照网络包的格式封装起来,发送到MII口;切换控制是用来选择控制信令通路或数据通路的开启;信令控制器解析信令,送往相应模块的配置端口;FIFO用于缓存上行数据和下行数据。

该模块主要完成两项工作:一是从MII口收发信令包,并将解析的信令送给各基带处理模块,进行参数配置和模式切换;二是从MII口收发数据包,提供上位机到FPGA内部各个基带处理模块之间的数据通路。

当系统在某种通信体制下正常工作时,上位机与FPGA之间的数据通路开启,同时完成双向数据的传输。待发送的下行数据经过解包、切换控制、FIFO_1传输到后续模块;接收到的上行数据经过FIFO_2、切换控制、打包传送到上位机。

当系统需要切换到另一种通信体制时,上位机与FPGA之间的信令通路开启,完成模块的重配置。配置信令经过解包、切换控制、信令控制后,解析出各配置参数送往相应模块进行参数重配置;待各模块配置完成后(mcu_reply有效),启动打包模块发送一个信令回执包以告知上位机。上位机收到FPGA的回执包后,系统已切换到新通信体制下,可以进行双向数据(上下行数据)的传输。

解包模块:从MII口获取网络包后,首先应核对网络包中D_MAC域的内容,若D_MAC域与本地MAC地址相同则接收该网络包,否则丢弃。然后取出网络包的Type域和Length域的内容,并根据Length域的长度信息取出包中的信令/数据,一并送往切换控制器。

切换控制模块:根据type端口的信息选择开启信令通路或者数据通路。当开启信令通路时,将从datain端口输入的信令送到信令控制器;同时当检测到mcu_reply端口的有效脉冲后,驱动打包模块发送一个特定格式的信令回执。当开启数据通路时,将从datain端口输入的数据送到FIFO_1;同时将从端口fout_data输入的FIFO_2的数据送到打包模块。

信令控制器:解析信令,并将根据配置信息完成模块的重配置。信令控制器在mcu_en端口为高电平期间从mcu_data读取信令,并开始按信令格式“AddrN+LenN+ParaN”解析信令。首先根据内部预设的一个模块端口查找表,查出AddrN对应模块的配置端口(包括configN_en,configN_data,configN_done)。配置时,configN_en为高电平,configN_data中传送的是配置信息(ParaN),configN_done在配置完成时会出现一个正脉冲。当信令控制器搜集完各个配置模块的config_done有效脉冲后,才输出一个mcu_reply有效脉冲反馈给切换控制器。

可重配置FIFO:缓存上行数据和下行数据,可以根据当前体制或业务需求来调整某些参数,以完成数据流的控制。例如FIFO一端连接的是固定的硬件网口速率(25 MHz时钟RXCLK/TXCLK),而另一端则需要实时改变数据速率,以匹配各种通信体制的上下行速率。本文中,可重配置FIFO中内嵌了一个参数可调的PLL,该PLL可以根据配置端口的config_data内容来实时改变时钟,因此FIFO能快速可靠地实现不同数据速率的切换。config_data的内容可以由用户在配置信令中自行设置,位宽为16 bit,可以完成216种不同速率(基本时钟为80 MHz,可以在基本时钟上倍频或分频)。

2 接口重配置过程的仿真

为了验证接口模块的正常传输数据的功能以及在线重配置的功能,对接口模块进行了仿真验证。仿真中,数据包的长度(即Length域)设置为1 490 B,Type1为080 A。信令包的长度(即Length域)设置为1 490 B,Type2为080 B,FIFO的配置信令长度设置为2 B。

仿真环境选用Modelsim,仿真中需要验证的场景是:

(1)初始配置过程,即在上电后,FPGA中的接口模块从MII口接收到第一个信令包(图6中信令1),信令控制器根据其中的信令信息完成FIFO1和FIFO2的速率参数rate1的配置,并反馈给MII口一个信令回执包。

(2)数据传输过程,即FPGA中的接口模块从MII口连续接收几个数据包(图6中数据1和数据2),数据通过切换控制器到FIFO1缓冲,再由rate1速率输出给后续的处理模块。

(3)在线重配置过程,即在系统工作中,FPGA中的接口模块从MII口接收到第二个信令包(图6中信令2),按(1)的过程配置FIFO的速率rate2,并反馈信令回执。

(4)新的数据传输过程,即同(2)的过程,数据由rate2速率输出给后续的处理模块。

利用TestBentch产生rxdv、rxd、r

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)