双供电DSP电源设计的总线冲突

时间:12-05

来源:互联网

点击:

TMS320F2812的内核和I/O采用双供电方式,在设计系统时必须保证如果其中的一种电压低于要求的操作电压,则 另一个电压的供电时间不能超出要求的时间。此外,在系统上电过程中,DSP需要根据相关的引脚电平对其工作模 式进行配置,因此要求内核要先于外部I/O供电。为了保障系统的稳定性和运行寿命,必须进行综合考虑,系统设 计过程中供电顺序也是其中设计之一。在上电过程中,系统内核供电要和I/O缓冲供电尽可能同时,这样可以保障I/O缓冲接收到正确的内核输出,并防止系统的总线冲突。

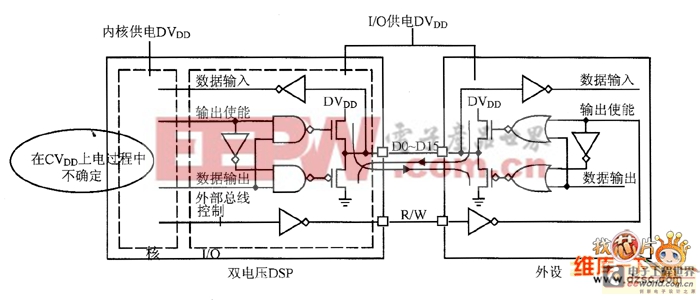

实际上在DSP系统设计时,防止DSP的IJO引脚同外设之间的总线冲突是系统设计的一个重要方面,需要控制内核和IJO的上电次序。由于总线的控制逻辑位于DSP内核模块,I/O供电先于内核供电会使DSP和外设同时配制成输出功能引脚。如果DSP与外设输出的电平相反将会产生总线冲突。图1给出了一个简单的双向口,此时会有较大的电流流过相反电平的通道。因此,系统设计时要求内核和外部I/O同时供电,从而避免总线控制信号处于不定状态时的冲突。如果内核先于I/O掉电,总线控制信号又处于不定的状态,也会导致有较大的电流流过I/O和DSP内核。因此,正确的上电、掉电次序(内核先上电后掉电)是保证系统可靠性,延长器件使用寿命的一种必要措施。

图1 双向端口总线冲突示意图

- 单片机RS-485多机通讯的实现(07-19)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)