JTAG接口的结构组成

时间:12-08

来源:互联网

点击:

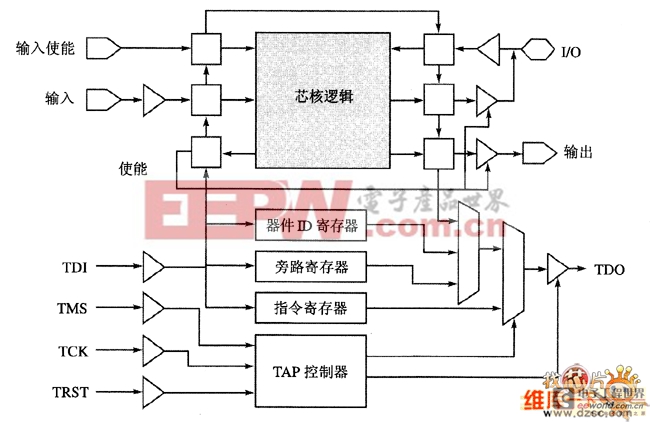

JTAG调试接口的结构如图1所示。它由测试访问端口TAP(Test Access Port)控制器、旁路(bypass)寄存器、指令寄存器和数据寄存器,以及与JTAG接口兼容的ARM架构处理器组成;处理器的每个引脚都有一个移位寄存单元,称为边界扫描单元BSC(Boundary Scan Cell),它将JTAG电路与处理器核逻辑电路联系起来,同时,隔离了处理器核逻辑电路与芯片引脚;所有的边界扫描单元构成了边界扫描寄存器BSR,该寄存器电路仅在进行JTAG测试有效,在处理器核正常工作时无效。

图1 JTAG调试接口示意图

(1)TAP(测试访问端口)控制器

TAP控制器对嵌入在ARM处理器核内部的测试功能电路的访问控制,是一个同步状态机,通过测试模式选择TMS和时钟信号TCK来控制其状态机。通过测试模式选择TMS和时钟信号TCK *控制其状态转移,实现IEEE1149.1标准所确定的测试逻辑电路的工作时序。

(2)指令寄存器

指令寄存器是串行移位寄存器,通过它可以串行输入执行各种操作的指令。

(3)数据寄存器组

数据寄存器组是一组串行移位寄存器。操作指令被串行装入由当前指令所选择的数据寄存器,随着操作的进行,测试结果被串行移出。其中:

·器件ID寄存器:读出在芯片内固化的D号。

·旁路寄存器:1位移位寄存器,用一个时钟的延迟把TDI连接至TDO,使测试者在同一电路板测试循环内访问其他器件。

·边界扫描寄存器(扫描链):截取ARM处理器核与芯片引脚之间的所有信号,组成专用的寄存器位。

JTAG接口 相关文章:

- 总线实现片内硬件调试支持单元设计(08-15)

- JTAG接口技术及ETM(11-21)

- ARM系统设计JTAG接口详细图解(11-10)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)