USB的总线结构

图1 USB总线的阶梯式星形结构

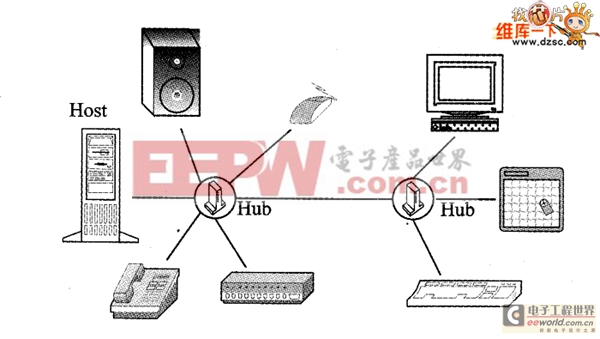

图2 USB总线的拓扑结构

在此的主机端通常是指PC主机。当然,主机端因具有根集线器,因此也含有集线器的功能。而集线器是在USB规范中特别定义出来的外围设备,除了扩增系统的连接点外,还负责中继(repeat)上端/下端的信号以及控制各个下端端口的电源管理。至于另一个设备,即是用户常见的外围设各。但在USB规范书中,称这种设各为“功能”(functiONs),意味着此系统提供了某些“能力”,例如具有键盘或鼠标等功能。当然不同的外围设各可以具有不同的功能。但基于使用上的习惯,用户在本书中都以设各称之。通过这种阶梯式星形的连接方式,最多可同时连接到127个设备。

此外,当USB 2.0与1.1的设各与集线器在一起使用时,如何才能呈现出最佳的USB 2.0高速带宽的特性?如图3所示,当USB 2.0与1.1规范的设各混合使用时,整个总线上交杂着高速/全速的设各与集线器。而如图4所示,惟有在USB 2.0集线器与USB 2.0设各的连接下,才具备高速总线带宽的特性。

图3 USB 1.1、USB 2.0设备与集线器-起工作的拓仆结构

图4 具备USB 2.0高速总线特性连接示意图

但用户可以试想一下,当PC主机开机前,已有一些外围设各连接上USB总线,那么PC是如何对所有连接至主机端的外围设各加以区分并寻址呢?

首先,PC一接上电源时,所有连接上USB的设各与集线器都会预设为地址0。此时,所有的下端端口的连接器都处于禁用且为失效的状态。然后,PC主机就会向整个USB总线查询。若发现第1个设各,比方说是鼠标,就将地址1分配给鼠标。然后再往下寻找第2个地址,且目前仍为0的设各或集线器。若发现是集线器,就将地址2分配给此集线器,并激活其所扩充的第1个下端端口的连接器。而后再沿此连接器一直往下寻找第3个地址,且仍为0的设各或集线器。这样重复地寻找与分配地址,直到所有的外围设各都赋予了新的地址,或已达到127个外围设各的极限为止。

这种过程类似于将各个设备分别加以列举的程序,称之为设各列举。当然,主机在配置新地址的同时,PC主机还要为每个新设各或集线器加载其所使用的驱动程序。

若在此时一个新的设各被接上,PC主机就会预设此设各为地址0,且PC就会确认并加载其相对应的驱动程序,并分配一个尚未使用到的新地址给它。而一旦某个设备突然被拔离后,PC可经过D+或D-差动信号线的电压变化来检测此设各被移除掉,然后就将其地址收回,并列人可使用的地址数值中。

- Linux系统下USB摄像头驱动程序开发(04-25)

- 基于uClinux嵌入式系统的汽车黑匣子的设计(07-08)

- 基于WinCE操作系统的通用USB数控键盘设计(08-05)

- 基于WinCE的ARM视频监控系统(11-14)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)