智能卡数据传输协议I2C总线

由于存储卡也是被同步时钟控制的,Pc总线很快就得以立足于芯片卡行业之中,大量的存储器可以在卡中 使用。下面的例子是基于SGS-ThornsON ST 24C04存储器芯片的,它有512字节的可自由读出或写人的EPROM 。对EEPROM编程的时闻安排由芯片内部处理,所以这方面不受外部控制。

I2C总线的硬件包括了在终端和卡之间的两条线,串行时钟SCL(Serial Clock)线传送时钟,其范围可达 100kHz,它产生的数据传输率高达100kb/s,对智能卡来说是比较高的,另一条线,串行数据SDA(Serial Data)线,用来双向交换卡和终端之间的数据。SDA线经一上拉电阻连接到终端的供电电源(Voc)。通信的 双方只能把这条线下拉至地。于是送出一高电平就毫无作用,这包括发送方把它的输出转换为高阻状态(三 态),而上拉电阻把SDA线拉至供电电压电平。

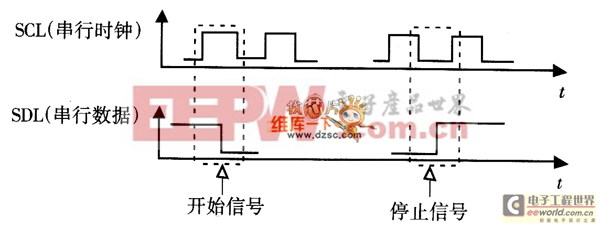

在智能卡的环境中,终端总是Pc总线为主而卡是从。数据传送总是按单字节打包,字节的最高位(第8位) 首先发送,每次在SDA线上的传送由开始信号启动并由停止信号结束,开始信号包括了在SDA线上的下降边而 此时在SCL线上的信号为高。相反,SDA线上的上升边而SCL线上的信号为低则指示出停止信号,参见图1。接 收方必须使SDA线接地一个时钟周期以便对每1字节的接收给以确认。

图1 I2C总线上的开始与停止信号

通信开始后,第1字节的头7位为接收方的地址。在我们的例子中,为了简单起见,我们假定地址的二进制 之值为1010000X。当然这可能随芯片的类型而改变,对某些存储器可在某限度内选择改变。地址中的最后一 位(x)向接收方指示是读出还是写入数据,1为读出而0则是写人。

下面的例子说明Pc总线用于智能卡时的一般功能。

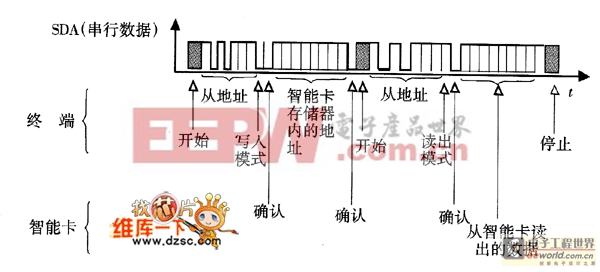

1)从一地址读出

对于从智能卡EEPROM的读出有几种类型的访问,此处所述类型为一次读出一字节,然而,也有可能从一列 中读出几个字节,如图2所示。

图2 用I2C总线从存储器读出一个字节

读序列由开始信号启动,接着各位含有卡的地址以及规定的写控制位。这向卡表明它必须立即把紧接的数据存储在内部缓存器中。这个缓冲器不过是EEPROM的面向字节的地址指针。卡接收到第1字节后,它把SDA线接地一个周期以示确认。而后,终端把EEPROM地址传送给卡,再一次,卡确认收到的数据。终端于是送出一个开始信号和卡的地址以及规定的读出位。接收到了这些,卡从指针给出的地址处取出数据送给终端。终端不需要对收到数据予以确认,它仅仅给卡一个停止信号,从而结束读出一字节的序列。

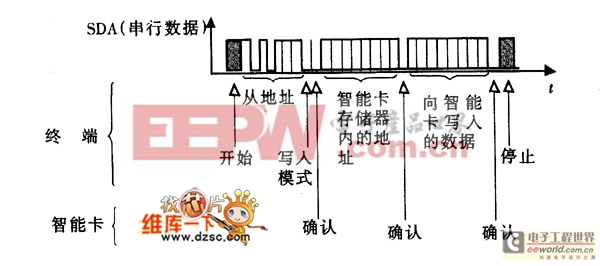

2)写人一地址

像从卡的EEPROM读出数据那样,写入数据也有不同的模式,它们中最简单的说明如下,用它可以在存储器中的任何地方写人单独的一个字节。

再一次,序列由终端的开始信号启动,紧接着卡的地址以及规定的写人位。卡确认收到后,从终端接收要写人数据的EEPROM的地址。

卡确认所有这些,于是接收数据。当终端收到第3次的确认,它表示卡已接收到了数据,便送出一个停止信号。接着,卡开始把收到的数据写人EEPROM,它不需要外部的定时信号。这样就结束了写入序列,而此字节已存人EEPROM,如图3所示。

图3 用I2C总线向存储器写人一个字节

- 利用低成本的MCU的UART驱动智能卡(05-04)

- JCVM中栈与帧的研究和设计(06-27)

- 非接触CPU智能卡技术(11-02)

- 使用32位MCU解决RFID智能标签/智能卡系统设计难题(10-15)

- 基于USB接口和智能卡的PKI 客户端设计(11-08)

- 利用现场总线设计电磁流量计智能卡(02-22)