基于ADSP-TS201S的二维DMA数据传输

图2中的Data0…Data3表示连续产生的4路并行数据,Data00…Data0n表示Data0的n个数据块。左侧表示为原始输入数据,例如A/D数据经过数字滤波器后的4路并行数据。中间表示为高速缓存区内部的一维排列数据,右边表示经过二维DMA链路口传输后的二维数据块排列。从图中可以看出,二维DMA传输将原来不适合DSP流水线操作的数据,实时高效地传输到DSP内部,并将数据块按照流水线要求顺序排列存储。

TS201的二维DMA控制和状态寄存器组,包括DMA控制寄存器、DMA状态寄存器、清除寄存器和传输控制寄存器等。通过对寄存器组编程可以允许相应DMA产生中断,整块数据传输完毕后,DMA将产生中断。中断发生在计数寄存器减至0,而且是最后一个数据单元传输后。每个DMA控制块都有自身的中断,DMA中断会锁存在ILAT寄存器中,并由IMASK寄存器打开。但需要注意的是,DMA中的计数器必须是减到零,向计数器寄存器写零并不会产生DMA中断。

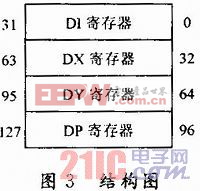

DMA传输控制块寄存器是一个128位的四字组寄存器,含有DMA块传输所需的控制信息。在DMA发送时,4个字包含了原数据的地址、将要发送的字数量、地址增量和控制位。在DMA接收时,4个字包含了目的地址、将要接收的字数据数量、地址增量和控制位,其结构如图3所示。

其中,DI寄存器是一个32位的DMA索引寄存器,它包括了将要发送或者接收的数据源地址或者目的地址,既可以指向内部寄存器和外部寄存器,也可以指向链路口。DX寄存器包含一个16位的汁数值和一个16位的修改量,计数值保存在高16位,修改量保存在低16位。如果使能了二维DMA,则该寄存器保存的只是X方向的计数值和修改量。计数值和修改量均以32位字为单位。DY寄存器和DX寄存器结合使用,该寄存器保存了Y方向上的16位修改量和16位计数值。如果只是进行一维的DMA传输,就不需要设置该寄存器。DP寄存器包含了DMA传输的所有控制信息。22位到31位包含了所有控制信息,0位到21位包含了链式信息。

一般情况下启动二维DMA的步骤如下:

(1)保存TCB DI寄存器中的当前地址,启动一个DMA存储器周期。

(2)在该周期内,将TCB DX增量寄存器中的X修改量与TCB DI寄存器中的当前地址相加。

(3)TCB DX计数寄存器内容减1,若TCB DX计数寄存器值为零,则执行第4步。

(4)重新加载TCB DX计数寄存器值。

(5)DMA寄存器中Y维增量加到TCB DI寄存器中的当前地址。

(6)TCB DX计数寄存器内容减1。

(7)若TCB DX计数寄存器值等于零,则DMA传输结束,在再次设置TCB前,需禁止它。

2 二维DMA应用

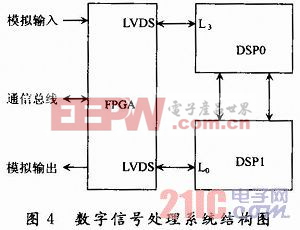

2.1 硬件设计

水声信号处理系统的复杂性和连续性要求信号处理系统具有较高的实时处理能力,所以设计时采用多片TS201来构成并行处理系统,以提高系统的数据处理能力。各DSP之间仅通过链路口无缝连接,片间连线少,降低了PCB布线难度和层数,节约了制板成本。此外,数据传输采用链路口的二维DMA方式,并不占用DSP内核的运算时间,可以提高处理板的实时性能,保证系统流水线操作的顺利执行。系统硬件结构图见图4所示。

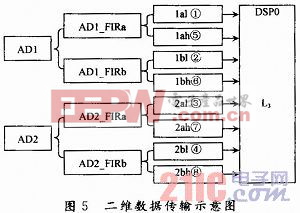

模拟输入端采用2片18位的高速A/D进行模数转换,每一片A/D的数据分别经过FPGA中的4个FIR滤波器,产生的8路并行数据通过链路口二维DMA传送给DSP组,进行相应的数字信号处理。具体数据传输框图见图5所示。

其中,①,②,…,⑧表示LVDS链路口数据传输顺序;lal表示AD1数据经过FIRa滤波器后的低1 KB数据,lah表示AD1数据经过FIRa滤波器后的高1 KB数据。滤波后的A/D数据进入乒乓缓存,最后通过链路口将数据传输到DSP内部。这里要求,在下一个数据块采样结束之前,需要完成上一个数据块的传输、滤波、相关及功率谱分析等一系列较为复杂的数据处理。由于AD1,AD2是同步采样的,经过数字滤波器的数据通过LVDS链路口顺序传输,为了减少数据块调整和挑选的时间,这里采用链路口的二维DMA传输方式,可以快捷地将A/D采集的数据块按照流水顺序写入DSP内部存储区。

2.2 软件设计

以图4中所示的FPGA与DSP0的L3链路口的二维DMA数据传输为例,假设数据块大小设定为1 024点,其链路口数据排列顺序如图6所示。

上标表示DSP0内部存储区内的偏移地址,每次DMA中断传输4×1 024个数据,即每次传输4行1 024列大小的数据,8次DMA中断即可获得一个时间片内的2个A/D采集数据经过4个FIR滤波器后的全部数据,而且数据块按照DSP0的流水线顺序排列。

DSP0软件需要完成L3链路口的初始配置和接受中断函数的设计,首先进行DSP系统时钟和UART及FIR滤波器系统的初始设置,然后进行二维DMA寄存器控制和内存块的分配,然后开启硬件A/D采集,等待二维DMA中断,进入中断后获得最终数据。软件流程见图7所示。

数据传输 DMA 二维 ADSP-TS201S 基于 相关文章:

- 基于 DSP-dMAX 的嵌入式 FIFO 数据传输系统设计(04-11)

- McBSP技术在数据传输中的应用(10-23)

- 基于DSP-dMAX 的嵌入式 FIFO 数据传输系统设计(11-27)

- 基于DSP的嵌入式 FIFO 数据传输系统设计(02-19)

- 基于DSP的CAN总线多节点远程数据传输系统(06-27)

- 嵌入式Linux的SOHO路由器电路设计(11-18)