DCM简介及其使用方法

Spartan-3 DCM的兼容性

S3 的DCM和 Virtex-II 以及pro的DCM 功能基本相同。但是S3 DCM的技术属于3代技术,因此在抗噪性能、相移能力方面有进一步提高。(客观的说,对我们的普通应用,不是特别重要。)

但是和Spartan-2系列相比,有很大改进。S2系列不叫DCM叫DLL,可见DFS和PS等功能完全是新加入的,所以S2系列其实除了二倍频几乎没有倍频和分频能力。从这点来讲,S3真的是用起来很爽了。DCM 输入时钟的限制

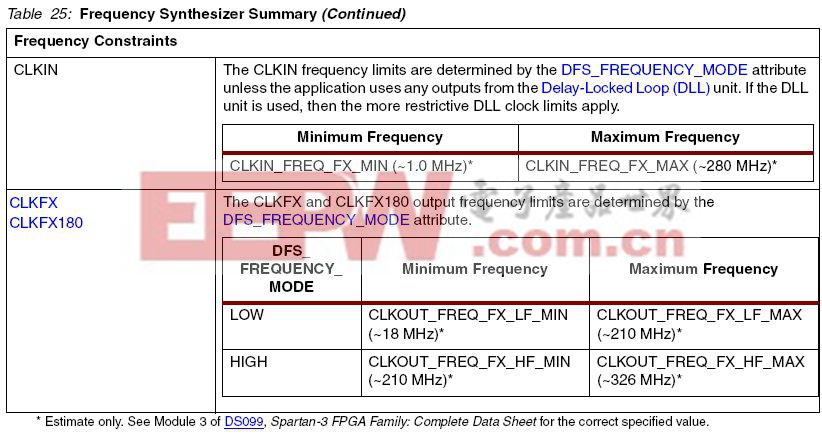

和所有物理器件一样,DCM的工作范围也是受限的。由于DLL和DFS的要求各不相同,因此DCM的输入频率的限制也视乎是否同时使用DLL和DFS还是单独使用其中之一。如果同时使用,则取限制较严格者作为整个DCM系统的限制。我们来看两者的独立限制。

呵呵,这部分内容不用记哦,需要的时候查一下软件或者手册就可以了。只要明白“CLKIN输入频率有限制,而且DLL、DFS同时使用时取其严格者” 这些道理就可以了。

除了时钟限制之外,对于时钟的质量也有一定限制,主要有3个:

1. CLKIN cycle-to-cycle jitter:约束了前后两个CLKIN周期的差异;

2. CLKIN period jitter:约束了100万个cycle中最大周期和最小周期之间的差异;

3. CLKFB path delay variation:约束了从外部进来的反馈回路的延迟波动,这种延迟波动在概念上其实和jitter如出一辙。

具体数值请查手册,知道有这么回事就可以了。LOCKED信号的行为方式

LOCKED信号用于指示整个DCM系统已经和CLKIN同步,从LOCKED信号有效开始,输出时钟才可以使用,在此之前,输出时钟可能会处于各种复杂的不稳定状态。我们来看一下LOCKED信号的行为状态机。

FPGA配置:

if (CLKIN已经稳定) next_state = 判断同步;

else next_state = RST_DCM;

判断同步:

if (已经同步) next_state = 判断同步;

else next_state = 同步失败;

同步失败: next_state = RST_DCM;

RST_DCM: next_state = FPGA配置;

现在来看看各个状态下的输出。

case (state)

FPGA配置: LOCKED = 0;

判断同步: LOCKED = 1;

同步失败: LOCKED = 0;

RST_DCM:LOCKED = 0;

endcaseRST 信号——重启锁定

RST信号用于在时钟不稳定或者失去锁定时,将DCM的相关功能重置,从而重新启动锁定追踪。

作为一个输入信号,RST无法被DCM自身置位,因此需要我们的应用设计来控制这个RST信号,否则需将其接地。

置位RST会将延迟tap的位置置0,因此可能会产生glitch或者是duty cycle 发生变化,另外相位偏移也会重置回到默认值。DCM 生成向导

安装了ISE就能得到一系列accessories。利用其中的Architecture Wizard 我们可以生成DCM模块。生成的DCM将产生3种输出:

1. 一个例化了DCM的逻辑综合文件(采用生产商特定格式的VHDL / Verilog)

2. 一个UCF文件控制特定实现

3. 所有其他用户设置都保存到XAW(Xilinx Architecture Wizard)文件中。

接下来描述一下向导使用步骤。

1. 从ISE或者Arch wizard中启动界面;

2. 第一个页面做基本配置:路径、XAW文件名、VHDL / Verilog选择、综合工具、FPGA型号;

3. 进行General setup,一看就明白,不细说,注意一下几点:

- CLKIN source 如果选 external 则 DCM 的 CLKIN 会自动连接到 IBUFG。

- Feedback如果选 internal 则反馈来自 BUFG。

4. 高级设置

- 选择FPGA的配置过程是否包含DCM的锁定,如果是,则配置完成信号DONE将在LOCKED信号有效后方能有效。

- 选择CLKIN是否要除2。由于DCM的输入频率有限,对于过高的输入时钟通过除2使之可用。

- Deskew调整,这个选项建议在咨询xilinx工程师后再使用。

5. 时钟输出口 Buffer 设置

- 默认情况下所有输出口都链接 BUFG 全局时钟网络入口

- 由于全局时钟网络的入口有限,用户可以定制时钟输出口连接到其他类型的Buffer

- Global Buffer:进入全局时钟网络的入口Buffer,共有4个,简称BUFG

- Enabled Buffer:还是上面的4个全局时钟Buffer,但是配置为有使能信号控制,简称BUFGCE

- Clock MUX:还是上面的4个全局时钟Buffer,但是配置为 2-to-1 MUX类型,由S信号控制选出,简称BUFGMUX

- Low skew line:没有buffer了,只能使用 skew 比较小的连线

- Local Routing:连到本地,skew的要求不是很严格

- None:禁止输出

- 对于Enabled Buffer类型和Clock Mux类型,需要指定En口的名字

- 需要为输出时钟信号指定名字或者使用默认

6. 设置DFS

- 设置目标输出频率,然后按calculate,自动生成 M/D 值和 Jitter 值

- 或者手动设置 M/D 值,然后按calculate,自动生成频率和 Jitter 值

7. 最后输出所需的3种文件。本文翻译自U

- #ifndef的使用方法详解(12-01)

- MDK使用方法与技巧(11-23)

- C8051F060内置高精度模/数转换器的使用方法(02-29)

- 基于C8051F060内置高精度模/数转换器的使用方法(11-12)

- 系统总线的组成及其特点(12-14)

- ARM嵌入式微处理器的发展及其面临的挑战(05-08)