卫星电视接收机控制的MCU实现方案

STC001是一种高性能、低成本的卫星电视接收机控制芯片。与传统ASIC实现方式不同,它以8位MCU配合软件的形式实现相关功能,相对于ASIC的一个明显优势是它可通过修改配备软件实现芯片的多种功能,适用于各种模拟卫星电视接收机控制。

目前,世界各发达国家的卫星电视早已直接进入家庭,部分国家的卫星电视用户覆盖率已超过50%,个体接收将成为卫星电视接收的主流。卫星直播的最大优势是只需1~2颗卫星,就可向无限数量的家庭用户直播上百套电视节目。中国人口众多但地区分布不均,且有线电视网不发达,因此是最适合发展卫星电视直播的国家。但是,由于中国现有政策和卫星电视发展水平的影响,中国的卫星电视用户覆盖率远远低于欧美发达国家的水平。随着人民生活水平的提高,消费者的购买力和收看卫星电视的需求越来越高,卫星电视机将是一个很有发展前景的产品。因此,作为卫星电视接收机核心的控制芯片,其发展前景也相当可观。

STC001的特性

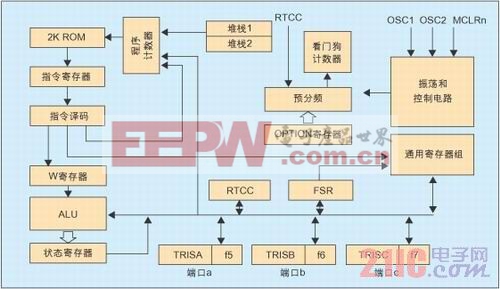

图1:STC001芯片的硬件结构示意图

STC001芯片能接收来自控制面板和遥控器的控制信号,然后根据收到的控制信号控制卫星电视接收机完成选台、面板显示、调频、调音,信号极化方向等智能化的操作。这些智能化操作主要是在内嵌MCU的基础上通过编写相应的程序来实现。随着产品的升级换代,还可以通过灵活地修改代码来实现各种新增功能,这是该芯片内嵌一个RISC CPU的最大优点。考虑到卫星电视接收机控制芯片所要实现功能的复杂性,程序空间被定为2KB。

RISC是近代计算机体系结构的一个里程碑。RISC处理器所设计的指令集以流水线处理方式高效地执行并使编译器产生优化代码,其特征如下:简单而且统一格式的指令译码;大部分指令可以单周期执行;只有LOAD/STORE指令访问存储器;简单的寻址方式;程序跳转延迟。正是基于这些特点,RISC CPU能够以比传统CISC架构小得多的电路实现相同的性能,从而具备面积小、速度快、功耗低等优势。

STC001芯片硬件结构如图1所示。整个芯片采用0.6微米工艺完成设计,强调功能单元模块化。版图设计的核心是减小面积、优化性能,因为逻辑采用了较新的设计思路,没有动态电路及特殊单元,所以版图设计主要偏重于如何以紧凑的设计减小面积。应着重注意的是时钟网络,由于该CPU采用4级时钟,为保证每一级时钟都能正常工作,在这四个时钟的驱动端加了比较大的缓冲并将缓冲器的MOS管宽长比作适当调整,使其上升沿和下降沿的延迟不相等,以保证四个时钟互不重叠。

ROM的设计及ROM编译器的研究

STC001芯片的ROM内部容量为2KB,字长为12位。由于批量定制产品的要求,ROM采用MASK结构。

为适应产品功能升级换代的需求,需要更改ROM码点完成产品换代。用手工填充码点所需时间长,可靠性也不能满足要求,因此自行开发了一个软件,以自动完成从程序到版图的全部过程。与常用的ROM编译器不同的是,这个软件是针对容量为2KB,字长为12位的ROM定制,ROM的框架完全由手工定制设计,可以重复利用,剩余的码点填充由程序自动完成。这样在保证效率的前提下生成的ROM具有很高的紧凑性。

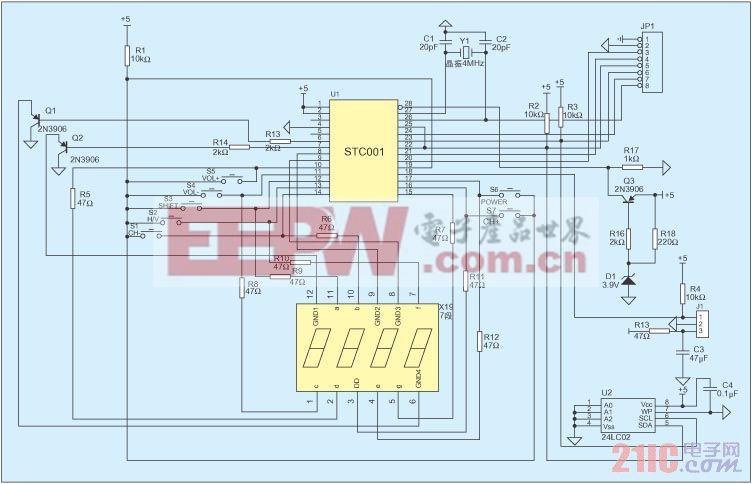

图2:STC001针对卫星电

视接收的应用电路图。

遇到的主要问题是系统整体仿真问题。虽然该MCU并不大,但也是一个小小的片上系统(SOC),其上集成了CPU、ROM、RAM及模拟电路(如上电复位和RC震荡器)。在这里采用分别仿真的办法。先用Artist仿真工具对模拟电路进行仿真,然后把仿真结果人工送入Verilog-XL进行数字全局仿真,最后从版图抽取LPE网表,用Star-Sim仿真软件进行全局后仿真。

STC001控制芯片的主要性能指标为:第一中频为479.5MHz,图象调谐范围为950M~2050M,步长1MHz,伴音调谐范围为5M~10M,步长10KHz,伴音中频为10.7MHz;具有4位共阳数码管驱动显示,可显示频道号、频率值、各种工作状态等;可存储120个频道值(配24C08 E2PROM);全静态CMOS,工作电压为3V~5.5V,晶振4MHz;此外STC001还具有预留天线方位角控制输出接口、完善的静音功能、天线选择功能、出厂频道参数预置功能以及水平/垂直极化方式选择等性能。

应用电路

图2是STC001针对卫星电视接收的应用电路,其中STC001的管脚10至17被按键扫描和LED显示驱动复用;管脚18脚接红外接收头的输出信号;管脚20至24将图象、伴音等控制信号输出到模块外;管脚22、23接MT24LC02,MT24LC02是E2PROM,处于可读写状态,用来保存一些必要的临时数据;管脚28接一个由5个器件组成的低电压复位电路。

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- DSP中DMA操作的无阻塞请求实现(06-18)

- 二维DCT编码的DSP实现与优化(09-08)

- 基于DSP处理器上并行实现ATR算法(01-29)

- 基于DSP的H.324终端设计(05-27)