用M-LVDS实现真正多点接口总线

多年来,业界已开发出多种成熟的技术用于在背板总线上传输信号。随着电信和数据通信业务量的不断增长,数据传输速度的不断提高,一些传统的单端和发射极耦合逻辑技术的局限性越来越明显。多点低电压差分信号(M-LVDS)是一种类似LVDS的接口标准,它可以为今天的总线应用带来高速、低功率和低EMI传输解决方案等优势,非常适合数据、控制、同步和时钟信号使用。

在目前的背板上,承载净负荷数据的高速信号一般走的是点到点(一个驱动器和一个接收器)接口,这些接口连接着各种内核芯片,如ASIC、FPGA、DSP等。正确端接的点到点接口可以为高速信号提供最佳性能,它们使用的信号电平可以是PECL、CML、VML和LVDS,速度可高达4Gbps以上,见图1。

LVDS的端接方法很简单,只需在接收器端放置一个端接电阻。LVDS也能处理多分支信号传输,即一个驱动器和多个接收器共享相同的差分传输线。M-LVDS是LVDS的扩展,允许多个驱动器共享相同的半双工总线。

LVDS(TIA/EIA-*A)是一个针对点到点和多分支应用的著名接口标准,可被看作是RS-422在速度上的升级。M-LVDS(TIA/EIA-899)则将LVDS的优势(高速、低功耗、低EMI、简单端接和工业标准)进一步扩展到了总线应用。它可被看作是RS-485在速度上的升级,用于通过背板(FR-4材料)走线或电缆进行传输的普通电信应用。M-LVDS可以提供极佳的信号完整性、热交换及内置故障防护支持。

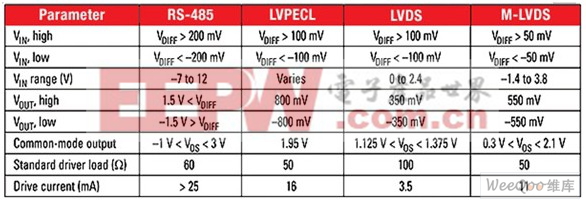

LVDS的驱动器输出电流为3.5mA,M-LVDS的驱动器输出电流是它的3倍,达11.3mA,并将输入电压门限从100mV减小到50mV,因此可以提供更好的信号完整性。对趋于标准化的多点应用而言,在总线两端放置100Ω的端接电阻可以形成有效的50Ω阻抗,信号电压摆幅可达565mV,相比之下典型的LVDS摆幅只有350mV。而对点到点的电缆应用来说,目前的IC输出级电路仍可以在单个100Ω终端上提供足够的电流,并产生900mV到1,000mV的电压摆幅,这个摆幅超过了800mV的LVPECL电平。

M-LVDS芯片可以用于速度高达125MHz的时钟和同步信号分配,也能用于速度高达250Mbps的数据和控制信号。

- Linux系统对ISA总线DMA的实现(06-19)

- DSP HPI口与PC104总线接口的FPGA设计(04-14)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 对TTCAN的分析(05-26)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)