为嵌入式应用选择合适的1-Wire®主机

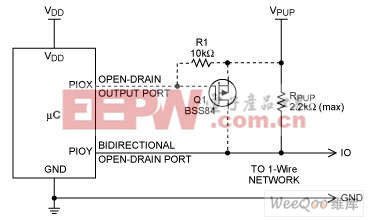

拉电阻。缺点在于,1-Wire时序通过软件产生,增加了前期软件开发的时间和成本。根据应用中1-Wire从器件数目和1-Wire上拉电压,需要其它端口引脚来实现强上拉。1-Wire总线最高工作电压取决于双向端口特性(最好具有5V容限)。1-Wire总线上挂接多个从器件时,RPUP值应取低一些。如果那样的话检查VOLmax是否与1-Wire从器件和微处理器端口的输入特性兼容。高速通信模式要求微处理器具备高时钟频率和/或较低的每指令周期时钟数。更多信息,请参阅应用笔记3829:确定多从机1-Wire网络的恢复时间和应用笔记126:用软件实现1-Wire通信。应用软件示例见1-Wire Public Domain Kit。

图1. 带可选强上拉电路(虚线部分)的双向端口引脚

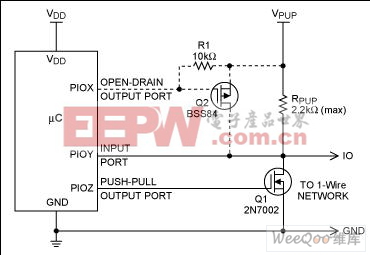

图2给出与图1类似的另一种基本电路。

图2电路的先决条件是需要两个备用单向端口、下拉晶体管及一定的程序存储器空间。电路的优点是不需要双向端口。缺点在于,1-Wire时序通过软件产生,增加了前期软件开发的时间和成本。根据应用中1-Wire从器件和1-Wire上拉电压,有时需要其它端口引脚提供强上拉。1-Wire总线最高工作电压取决于双向端口特性(最好具有5V容限)。1-Wire总线上挂接多个从器件时,RPUP值应取低一些。此时,应检查VOLmax是否与1-Wire从器件和微处理器端口的输入特性兼容。高速通信模式要求微处理器具备较高的时钟频率和/或较低的每指令周期时钟数。更多信息请参阅应用笔记3829:确定多从机1-Wire网络的恢复时间和应用笔记126:用软件实现1-Wire通信。应用软件示例见1-Wire Public Domain Kit。

图2. 带可选强上拉电路(虚线部分)的单向端口引脚

2类. 内置1-Wire主机的微控制器

图3电路与图1非常类似,不同之处在于微控制器类型。

图3电路的主要前提是需要一个内置1-Wire主机的微控制器,如DS80C400、DS80C410或DS80C411,以及一定的程序存储器空间。电路的优点在于1-Wire时序由硬件产生,可以减少前期软件开发的时间和成本。因此,整个应用软件可以用高级语言编写。DS80C400系列微控制器端口带有5V容限。缺点在于,只有高端微控制器才内置有1-Wire主机。根据应用中1-Wire从器件和1-Wire上拉电压,可能需要其它端口引脚提供强上拉。1-Wire总线上有不止一个从器件时,RPUP值应取低一些。此时,应检查VOLmax是否与1-Wire从器件和微处理器端口的输入特性兼容。更多信息,请参阅应用笔记3829:确定多从机1-Wire网络的恢复时间、应用笔记613:DS80C400的Keil C语言编程、以及DS80C400数据资料。应用软件示例见1-Wire Public Domain Kit。

图3. 内置1-Wire主机的微控制器及可选的强上拉电路(虚线部分)

3类. 合成的1-Wire总线主机(ASIC/FPGA)

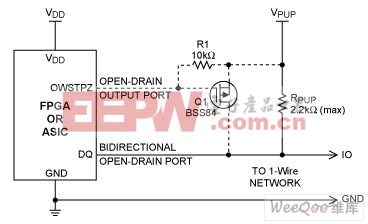

图4电路与图3非常类似。不同之处在于微控制器和1-Wire端口是内置在ASIC或PFGA中的。

图4电路的主前提是需要具有单片机能力的ASIC或FPGA,至少有一个空闲的双向端口引脚,3470个未使用的门和一定的程序存储器空间。电路的优点在于1-Wire时序由硬件产生,可以减少前期软件开发的时间和成本。因此,整个应用软件可以用高级语言编写。缺点在于,并非所有ASIC或FPGA都有5V容限端口。1-Wire工作电压取决于ASIC/FPGA的端口特性。一些2.5V FPGA有5V容限I/O端口,比3.3 FPGA理想。根据应用中1-Wire从器件和1-Wire上拉电压,可能需要其它端口引脚提供强上拉。1-Wire总线上挂接多个从器件时,RPUP值应取低一些。此时,应检查VOLmax是否与1-Wire从器件和微处理器端口的输入特性兼容。更多信息请参阅应用笔记119:嵌入1-Wire主机、应用笔记120:利用1-Wire主机通讯、应用笔记145:Interfacing the Maxim 1-Wire Master (DS1WM) to an ARM7 Processor、应用笔记3829:确定多从机1-Wire网络的恢复时间、以及DS1WM数据资料。欲获取1-Wire主机Verilog/VHDL代码,请通过提交技术支持要求。应用软件示例请参见应用笔记120和145。

图4. 带可选强上拉电路(虚线部分)的ASIC/FPGA

4类. 串行接口协议转换

图5电路只需一个额外器件即可构建一个功能齐备的1-Wire主机。

图5电路的主要前提是需要一种控制UART的方式,例如微控制器、FPGA或PC串行端口,还需要一定的程序存储器空间。电路的优点在于1-Wire时序由硬件产生,可以减少前期软件开发的时间和成本。因此,整个应用软件可以用高级语言编写。1-Wire时序可以通过控制寄存器微调。DS2480B支持强上拉和有源上拉。嵌入式应用不需要对1-Wire时序和有源上拉进行微调,不过,内置的4位搜索加速器使1-Wire ROM搜索在软件中更易实现。就缺点而言,DS2480B较图1至图4中的分立元件昂贵。DS2480B仅采用5V工作电

- 高速PCI信号采集卡设计与实现综合实例之:主机应用程序和驱动程序的接口设计(06-04)

- 总线报警主机红外光栅视频联动系统(12-14)

- RS485如何实现多主机控制(12-14)

- RS-485的多机通信程序(主机端)(11-30)

- 新唐M0的MDK+NU-LINK的半主机调试使用(11-29)

- 第45节:主机的串口收发综合程序框架(11-22)