DSP芯片功能的扩展简介

令支持用于视频压缩算法(如MPEG2、MPEG4和JPEG)的运动估算算法。

这种架构处理多长度指令编码。非常常用的控制型指令被编码为紧凑的16位字,更多算术密集的信号处理指令编码为32位值。处理器将16位控制指令与32位信号处理指令混合并连接成6?位组,以使存储器容量最大化。缓冲和取指令时,内核完全自动挑选总线长度,因为内核没有调整约束。

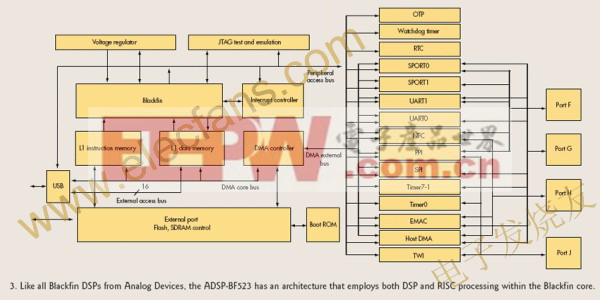

所有Blackfin处理器,如ADSP-BF523,都包含独立的DMA控制器,支持自动数据传输,而对处理器内核的操作压力很小(图3)。DMA传输可发生在内部存储器与许多具备可直接存储器存取(DMA)功能外设的任何部分之间。传输也能发生在外设和接至外部存储器接口的外部器件之间,包括SDRAM控制器和异步存储控制器。

存储器架构包括L1和L2存储器块。L1存储器直接连接到处理器内核,以全系统时钟速度运行,为时间关键的算法部分提供最佳系统性能。此外,L1存储器也可配置为SRAM、高速缓冲存储器或者两者的组合。

通过同时支持SRAM和高速缓冲存储器编程模型,系统设计师可分配关键的要求高带宽和到SRAM低存取的实时信号处理数据集合,同时在高速缓存中存储“软”实时控制和操作系统(OS)任务。L2存储器是一更大的大容量存储器存贮区,性能稍有降低,但仍快于片外存储器。

每个Blackfin处理器都采用了多种功率节省技术,这些技术都是基于选通时钟内核设计,可以在逐条指令的基础上选择性地降低功能单元功率。针对需要很少或不需要CPU活动的周期,这些处理器也支持多种降低功率模式。

在这种自约束动态功率管理方案中,可独立控制工作频率和电压,满足当前执行算法的性能要求。大多数Blackfin处理器提供片上内核稳压电路,提供低至0.8V电压工作,特别适合要求电池寿命延长的便携式应用。

Blackfin处理器可配合多种微控制器型外设,包括10/100Ethernet MAC、UARTs、SPI、CAN控制器、支持脉宽调制(PWM)的定时器、看门狗定时器、实时时钟以及无缝的同步和异步存储控制器。

多核DSP

飞思卡尔的MSC8144 DSP就是一个好的多核DSP的例子,MSC8144 DSP是基于该公司的的StarCore技术,即特定的第三代SC3400 DSP内核。

这种芯片集成了4个DSP子系统。每个子系统内都有SC3400 DSP内核、16k字节L1指令高速缓存、32k字节L1数据高速缓存、存储器管理单元(MMU)、扩展的可编程中断控制器(EPIC)以及两个通用32位定时器。子系统支持调试和整形,具有低功率“等待”和“停止”处理模式。每个DSP内核运行速率高达1GHz,因此此芯片的性能与4GHz单核DSP的性能相当。

MSC8144还包含该公司的QUICC引擎技术子系统,包括两个RISC处理器、48k字节多主机RAM以及48k字节指令RAM。这种子系统支持三个通信控制器,具有一种异步传输模式(ATM)和两个吉比以太网接口。它也可以从DSP核下载预先安排的任务。

ATM控制器在UTOPIA/PO模式下以25/50MHz支持UTOPIA II级8/16位,适应层支持AAL0、AAL2和AAL5。两个以太网控制器仅使用一个1000Mbit/s数据率4引脚串行器/并行器(SERDES)接口,通过MII/RMII/SMII/RGMII/SGMII和SGMII协议即可支持10/100/1000Mbit/s工作。

与前面提到过的DSP芯片一样,这种芯片的DSP和QUICC子系统的外围有存储器、接口和I/O。至于存储器,芯片包含128k字节L2共享指令缓存、用于关键数据和临时数据缓冲的512k字节M2存储器、96k字节引导ROM和一个庞大的10M字节128位宽M3存储器。

芯片上也有DDR和DMA控制器。DDR控制器具有高达200MHz的时钟(400MHz数据率)和16/32位数据总线。以

一或两个组,支持高达1G字节的DDR1和DDR2。DMA控制器具有16个双向通道,高达1024缓冲描述符和可编程优先权、缓冲器和多路传输结构。

芯片级判优与开关系统(CLASS)提供处理部件(和其他启动程序)与目标(如M2存储器、DDR SRAM控制器和器件配置控制和状态寄存器)之间的全部的制作非模块化判优。

MSC8144支持下一代及传统接口,如双吉比以太网、Serial RapidIO互连、UTOPIA、PCI以及分时多路复用(TDM)。

Serial RapidIO 1×/4×端点符合RapidIO贸易协会的规范1.2。它支持读、写、信息、门铃、入站模式的维护接入以及出站模式的信息和门铃。PCI接口遵守PCI规范修订版2.2,以33或66MHz读写所有PCI地址空间。

多达8个片上独立的TDM模块提供的特征有可编程字大小(2、4、8或者16位)、基于硬件的A法则/μ法则转换、所有通道的数据率都高达128Mbit/s、与E1、或T1帧调节器无缝接口、与H-MVIP/H.110设备、TSI和编解码器如AC'97的接口能力。

由于有多核架构和下一代及传统接口,MSC8144DSP非常

- VHDL:中文版Verilog HDL简明教程:第1章 简介(06-06)

- RS-485接口简介(12-20)

- I2C之知(一)--I2C的简介和特性(12-15)

- RS485简介(12-14)

- Android 框架简介(09-12)

- 温、湿度采集系统的硬件设计简介(11-09)