闪存微控制器的“新闪存”架构技术

简介

嵌入式微控制器越来越多样化,可以满足嵌入式系统市场的应用需求,而主流已经从传统的掩模ROM微控制器转向了内置闪存(可擦写的非易失性只读存储器)的闪存微控制器。

闪存微控制器目前有两种主要应用:CPU程序代码存储和包含用户信息和更新信息的数据存储。这两种应用所需的属性各不相同:程序代码存储的编程/擦写次数少,而数据存储的编程/擦写次数多。采用1晶体管型浮栅单元技术,富士通半导体可以提供这两种不同的属性,并能实现高可靠性:程序代码存储能够将数据保存20年;数据存储能够擦写10万次。

近年来,由于嵌入式系统的性能越来越高,导致市场对于能够降低环境负荷的生态技术的需求也日益增加。针对这些市场需求开发闪存宏成为一个挑战。尽管通过使用突发模式可以实现加速,但是由于存在“等待时间”,仍然会有很多问题,因为“等待时间”由不同的命令产生,而闪存微控制器是进行实时处理的,因此会导致性能越来越差。

“新闪存”架构

将富士通半导体专有的高速存储器存取技术——快速循环随机存取存储器(FCRAM)电路技术应用于富士通半导体高度可靠的NOR型闪存技术,可以实现“新闪存”架构,由此产生兼具高可靠性和低功耗双重性能的闪存宏。

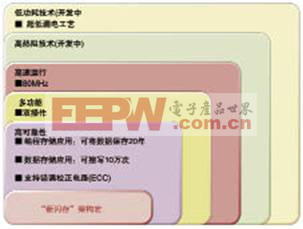

图1 显示了“新闪存”架构技术的特点。

图1 “新闪存”架构技术的特点

有了“新闪存”架构技术,富士通半导体可以通过优化单元阵列降低驱动负载,这是FCRAM电路技术的特点。还通过一种自行设计的电源电路技术和数据读取方法的加速,实现了访问字线电压的高速启动。通过这些设计,存取速度可以高达10ns/MHz(传统产品的2.5倍),而工作电流损耗则低至9μA/位(传统产品的三分之一)。

生态闪存微控制器有助于进一步降低环境负荷

一般来说,电流损耗会随着工作频率的增加而变大。追求高频会导致工作电流损耗的增加及环境负荷的加大。

图2显示了“新闪存”架构技术在闪存微控制器中的应用实例。

图2 内置“新闪存”架构的生态微控制器实例

即便嵌入式微控制器的性能(随机存取)提升了两倍,工作电流仍可以被压缩三分之二,因此可以同时实现性能提升和生态保护。

未来发展

图3显示了富士通半导体的闪存技术路线图。

图3 闪存技术路线图

富士通半导体将继续开发工作,把超低漏电工艺和高热阻技术列入开发计划(这是正在开发的环保技术),并且将“新闪存”架构闪存宏作为富士通半导体生态技术的核心。通过提供采用这些生态技术的闪存微控制器,富士通半导体可以为汽车市场提供高可靠性、高温支持和高速运行,从而降低嵌入式系统的环境负荷。

- 用NiosII搭建的固态盘设备系统(03-23)

- DSP和Flash接口技术的实现(08-15)

- 基于闪存TMS320VC5409DSP并行引导装载方法(07-05)

- 从NAND闪存中启动U-BOOT的设计(05-16)

- 3D NAND这么火,比2D NAND到底优秀在哪?(01-08)

- STM32 产品唯一身份标识寄存器(96位) 闪存容量寄存器(11-13)