基于DSP的无人值守地面探测系统硬件设计

转换。一旦转换开始,DSP必须等到转换完成才能选择另外一个通道或者初始化另外一次新的转换。ADC不会向DSP发出中断信号,所以DSP只有通过查询ADC数据寄存器(ADCdata)的ADCBusy位来获取ADC的状态。当转换完成时,ADCBusy由1被置为0,表示转换数据已经存放在数据寄存器ADCData中,然后DSP能够从ADCData读取数据。ADCData中也包含寄存器ADCctl中表示多路选择器通道选择值的ChSelect的值,所以DSP能够鉴别是从哪个通道获取的采样值。

(2)外设控制和扩展芯片的选型

本系统的可编程逻辑器件需满足上电即可工作,其作用是作为DSP外设控制和扩展的芯片,设计的组合逻辑比较多,因此首选CPLD。随着大规模可编程器件的发展,采用DSP+CPLD结构的信号处理系统显示出了优越性,该结构具有结构灵活,通用性较强,适于模块化设计,易于维护和扩展。

可编程逻辑器件(CPLD)采用ALTERA公司的EPM570T100C5N来实现系统的接口逻辑。该逻辑器件采用FPGA结构,配置芯片集成在内部,和普通PLD一样满足上电即可工作。

(3)集成运放的选型

地震动传感器需探测200m以内的运动车辆及20m以内人员脚步的信号,声音传感器需感应600m以内的车辆噪声(探测距离与传感器的灵敏度关系非常密切)。在如此远距离情况下,由传感器检测得到的目标信号很微弱,通常只有毫伏级。如此小的信号必须先经过前置放大和预处理后才能进行采集处理。另外,信号放大处理电路功耗应尽量小。

由于原始信号极其微弱,很容易被噪声所淹没,为了能有效抑制干扰,设计选用美国TI公司生产的OPA4336运算放大器,它的内部集成了四个运算放大器,具有精度高、功耗低等特点。

(4)其他器件的选型

SDRAM选用HY57V641620ETP,FLASH选用S29AL800D;选用78M05(12V-5V电压转换芯片)作为辅助芯片。

DSP系统设计

DSP工作模块设计

在此主要介绍硬件电路设计,通常是指以DSP为中心的外围电路设计,包括前向通道(输入数据通道)和后向通道(输出数据通道),以及复位电路、电源设计等。DSP工作模块原理如图2所示。

图2 DSP工作模块原理框图

DSP系统采用四节3V高效能电池串联供电(供电电压DC12V),采用78M05转换出来的DC5V,再由TLV1117-3.3和TLV1117-ADJ稳压芯片提供的3.3V与1.6V两种电压作为DSP的工作电压,并用JTAG口硬件仿真并下载程序,SDRAM用于动态存储采集到的数据,FLASH保存DSP运行程序,待复位后重新载入DSP内部RAM中运行,CPLD负责外围器件的选择控制。DSP通过16根数据线和14根地址线与SDRAM、FLASH、CPLD进行通信。DSP作为系统的核心,完成信号采集、过零数分析、短时能量分析、功率谱相似性识别算法等处理过程。

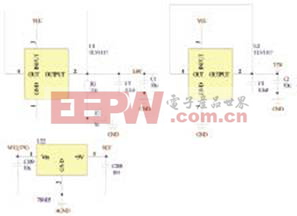

系统电源模块设计

主系统额定输入电压DC12V,78M05(图3中U22)转换出DC5V(供无线通信模块使用)再由TLV1117-3.3(图3中U2)和TLV1117-ADJ(图3中U1)转换DC3.3V和DC1.6V供DSP系统使用,系统电源电路如图3所示。

图3 系统电源电路图

由于本系统需要将采集到的信号做信号分析和变换等工作,对DSP的时钟信号有较高的要求,因此采用12M有源晶振作为DSP系统工作时钟源。DSP等各个芯片的滤波电容均放置于芯片的底层,一方面可以节省顶层布线空间,另一方面可以较好地滤除电源产生的毛刺等干扰信号。另外将10uF和0.1uF的电容交叉放置可以产生更好的滤波效果,系统晶振与DSP的滤波电容电路如图4所示。

图4 系统晶振和DSP的滤波电容电路图

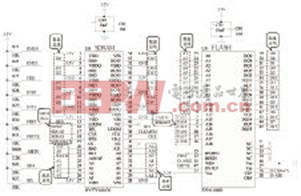

DSP与SDRAM和FLASH的接口电路设计

本系统硬件设计中涉及较多的DSP与存储器的连接与访问。TMS320VC5509A的外部存储器接口除了对异步存储器的支持以外,还提供对同步突发静态存储器(SBSRAM)和同步动态存储器(SDRAM)的支持。异步存储器可以是静态随机存储器(SRAM)、闪存等存储设备,也可以是A/D转换器件、并行显示设备等。DSP与SDRAM和FLASH的接口电路如图5所示。

图5 DSP与SDRAM和FLASH的接口电路图

存储模块的设计

DSP既可将SRAM作为程序存储器,也可作为数据存储器。本系统用FLASH存放程序,在系统运行时,为提高运行速度,需将程序从FLASH搬至快速SRAM中运行,此时SRAM地址映射在程序空间中,而当系统的数据存储空间超过内部RAM时,SRAM地址映射在数据空间中。系统采用HY57V641620型动态数据存储器SDRAM作为SRAM。

为了充分发挥DSP性能,在加电后需要将用户代码装载到高速RAM存储器中运行。FLASH存储器是一种高密度、非易失性的电可擦写存储器,存储量大,使用方便,适用于低功耗、高性能的系统。设计FLASH与DSP的接口时,FLASH的数据线和地址线分别和DSP的外部数据和地址总线相连,FLASH的分页控制位A[13:1

系统 硬件 设计 探测 地面 DSP 无人 值守 基于 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)