嵌入式GIS地图快速显示方法的应用

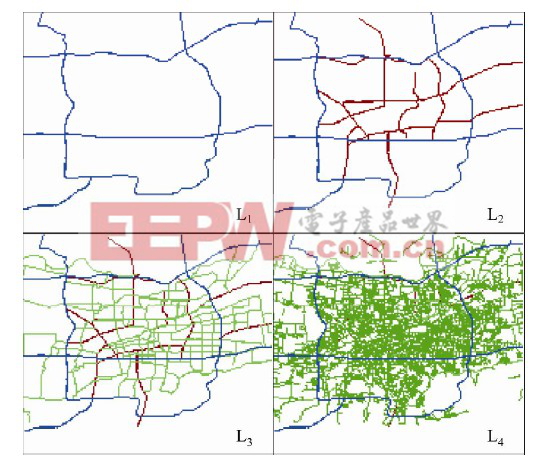

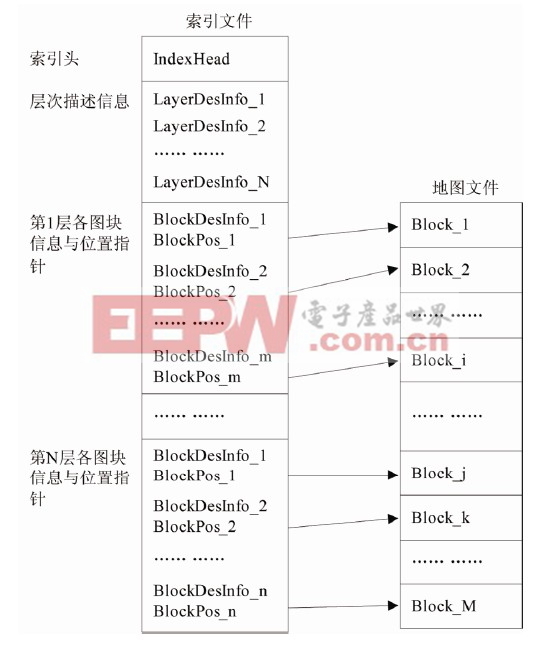

到什么程度时, 才显示该图层。 划分的地图数据层次依次记为L1, L2, L3, …, 其中L1 记录地图中最主要的地理要素,L2记录次重要的地理要素, L3记录一般性地理要素, 依此类推。 实际操作时, 对地图数据分层处理显示参数的确定非常重要, 其选择的优劣直接影响地图显示效率。 本文依据地理要素的属性, 按照以下原则确定显示参数将: ① 对于基础地理要素, 如道路、桥梁、河流、行政区边界等, 在国家标准《基础地理信息要素分类与代码》中采用要素编码区分了其重要性特征, 可以参考其要素编码设定显示参数;② 对于非基础地理要素, 如学校、酒店、商业街区、街区居民地等, 其重要性特征没有统一的标准, 则根据这类地理要素自身包含的等级属性, 如酒店星级、街区面积等来确定显示参数。 以某城市公路网为例, 采用道路要素编码为显示参数进行分层处理, 可分为4 个层次: L1 记录城市一级、二级道路: 高速公路及环线; L2 记录城市三级道路: 市内主干道, L3 记录四级道路: 市内次干道, L4 记录城市五级道路: 市区分支街道。 地图显示时, 不同层次细节显示需要在上一层次显示的基础上读入相应Li 的数据集合来支持, 如图2 给出某城市公路网L1~L4 的显示效果。 图2 某城市公路网不同层次显示效果图 3.3 矢量地图数据分块方法 要提高地图的显示速度, 应尽量减少地图非屏幕显示区域的数据量, 因此需对矢量地图进行分割形成地理范围更小的图块, 并将图块作为嵌入式GIS 系统地图数据处理的基本单元。 对于矢量数据的分块方法分别是对点、线、面的矩形分割, 即将地图数据根据屏幕显示范围大小横向分为N 份, 纵向分为M 份, 形成由N×M 个同等大小的基本地理单元组成的图块集合。 地图显示时, 系统只需根据显示层次读入与显示覆盖区域相交的部分图块, 快速将地图绘制在屏幕上。 在对地图数据进行分块处理时, 需要重点考虑分割图块的大小。 因为一定矢量数据划分的图块较大, 则读入内存的非屏幕显示区域的数据就会越多, 增加了不必要的冗余数据; 而数据划分的图块越小, 读取数据的准备时间就越长, 且对矢量数据的分割还会增加显示的数据量, 也会影响显示速度。 因此在数据分块时要根据实际屏幕显示尺寸和地图比例尺综合考虑分块大小。 若已知屏幕分辨率为L×W 像素, 地图的比例尺为1:S, 地图经度覆盖范围X, 纬度覆盖范围Y, 地图表示精度记为A, 地球圆周单位秒代表距离为m (m 为常量, m ≈31 米), 记地图横向划分图块数量为N, 纵向划分图块数量为M, 则有以下公式: 其中, X, Y 单位为秒, A=0.1×10-3×S. 以比例尺为1:50 000, 经度范围25', 纬度范围15' 的矢量地图和800×480 的屏幕为例, 可由式(2)推导得该地图应划分为12×12 块图块。 3.4 矢量地图网格索引 如前文所述, 提高地图显示速度还必须使地图显示时能快速的从外存检索和调度当前显示范围所涉及的矢量数据, 因此还需建立空间索引。针对逐层分块的地图组织策略, 建立了基于文件存储的网格索引。 基于文件的网格索引以索引文件存储索引数据, 通过名为POSITION 的位置指针可以对每个空间目标的首地址进行快速定位, 具有操作简洁、直接访问、适应广泛的优点, 其索引结构如图3 所示。 图3 基于文件的网格索引结构图 索引数据按地图层次存储, 每层索引数据与相应的地图分层数据对应。 索引数据结构包括索引头、层次描述信息和每层划分图块索引: 索引头主要包括该地图数据的名称、编号和划分层数; 层次描述信息包括各层次的编号、左下角点坐标、分块的宽度和高度、分块的行数和列数以及该层图块索引在索引文件中的位置; 图块索引内容主要包括图块数据在地图数据文件中的位置指针及其地理要素概要信息, 包括标识、要素类型编码、外接矩形、占用存储空间大小等。 建立网格索引后, 地图显示时系统首先计算出当前层次覆盖显示区域的图块; 然后根据每个图块的地理要素信息进行重复显示判断, 过滤掉已经显示的地理要素; 再根据位置指针, 从地图文件中读取该图块的矢量数据, 进行显示处理。 因此网格索引能直接过滤掉非屏幕显示区域图块及地理要素, 极大地减少地图数据的读取量, 并通过索引文件中的POSITION 指针直接从地图文件中查找到矢量数据, 有效缩短了检索时间。 4 性能测试与分析 为验证本文设计的嵌入式GIS 地图快速显示方法的有效性, 本文选择UT6410 开发板搭建嵌入式试验平台进行了测试。 实验平台拥有主频667MHz 的ARM处理器、128MB 内存

- 基于FPGA的DSP设计方法(08-26)

- 专家指导:Linux操作系统密码恢复方法(05-16)

- 基于多核DSP Bootload代码加载方法研究(01-16)

- 基于DSP 的大容量无线传输技术中高性能的启动方法(03-16)

- 多核调试新方法探讨(10-22)

- 有备无患Linux操作系统备份方法介绍(06-06)