8051单片机原理

8051是MCS-51系列单片机的非常典型的产品,我们用这一个代表性的型号进行系统的单片机原理讲解。

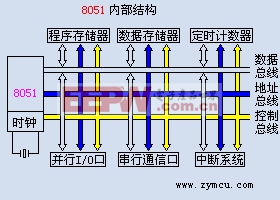

8051单片机包含中央处理器、数据存储器(RAM)、定时/计数器、程序存储器(ROM)、并行接口、串行接口和中断系统等几大单元及数据总线、地址总线和控制总线等三大总线,现在我们分别对其原理加以说明:

·数据存储器(RAM):

8051内部有128个8位用户数据存储单元和128个专用寄存器单元,它们是统一编址的,专用寄存器只能用于存放控制指令数据,用户只能访问,而不能用于存放用户数据,所以,用户能使用的的RAM只有128个,可存放读写的数据,运算的中间结果或用户定义的字型表。

·中央处理器:

中央处理器(CPU)是整个单片机的核心部件,是8位数据宽度的处理器,能处理8位二进制数据或代码,CPU负责控制、指挥和调度整个单元系统协调的工作,完成运算和控制输入输出功能等操作。了解中央处理器cpu对于弄懂单片机原理非常的重要。

·程序存储器(ROM):

8051共有4096个8位掩膜ROM,用于存放用户程序,原始数据或表格。

·全双工串行口:

8051内置一个全双工串行通信口,用于与其它设备间的串行数据传送,该串行口既可以用作异步通信收发器,也可以当同步移位器使用。

·中断系统:

8051具备较完善的中断功能,有两个外中断、两个定时/计数器中断和一个串行中断,可满足不同的控制要求,并具有2级的优先级别选择。

·时钟电路:

8051内置最高频率达12MHz的时钟电路,用于产生整个单片机运行的脉冲时序,但8051单片机需外置振荡电容。

·并行输入输出(I/O)口:

8051共有4组8位I/O口(P0、 P1、P2或P3),用于对外部数据的传输。

·定时/计数器(ROM):

8051有两个16位的可编程定时/计数器,以实现定时或计数产生中断用于控制程序转向。

单片机原理有两种,一种是程序存储器和数据存储器分开的形式,即哈佛(Harvard)结构,另一种是采用通用计算机广泛使用的程序存储器与数据存储器合二为一的结构,即普林斯顿(Princeton)结构。INTEL的MCS-51系列单片机采用的是哈佛结构的形式,而后续产品16位的MCS-96系列单片机则采用普林斯顿结构。

下图是MCS-51单片机原理图。

■ MCS-51单片机的关键引脚说明:

MCS-51系列单片机中的8031、8051及8751均采用40Pin封装的双列直接DIP结构,右图是它们的引脚配置,40个引脚中,正电源和地线两根,外置石英振荡器的时钟线两根,4组8位共32个I/O口,中断口线与P3口线复用。现在我们对这些引脚的功能加以说明:

8051的复位方式可以是自动复位,也可以是手动复位,见下图。此外,RESET/Vpd还是一复用脚,Vcc掉电其间,此脚可接上备用电源,以保证单片机内部RAM的数据不丢失。

特殊功能寄存器 初始态 特殊功能寄存器 初始态

ACC 00H B 00H

PSW 00H SP 07H

DPH 00H TH0 00H

DPL 00H TL0 00H

IP xxx00000B TH1 00H

IE 0xx00000B TL1 00H

TMOD 00H TCON 00H

SCON xxxxxxxxB SBUF 00H

P0-P3 1111111B PCON 0xxxxxxxB

·Pin31:EA/Vpp程序存储器的内外部选通线,8051和8751单片机,内置有4kB的程序存储器,当EA为高电平并且程序地址小于4kB时,读取内部程序存储器指令数据,而超过4kB地址则读取外部指令数据。如EA为低电平,则不管地址大小,一律读取外部程序存储器指令。显然,对内部无程序存储器的8031,EA端必须接地。

在编程时,EA/Vpp脚还需加上21V的编程电压。

·Pin30:ALE/当访问外部程序器时,ALE(地址锁存)的输出用于锁存地址的低位字节。而访问内部程序存储器时,ALE端将有一个1/6时钟频率的正脉冲信号,这个信号可以用于识别单片机是否工作,也可以当作一个时钟向外输出。更有一个特点,当访问外部程序存储器,ALE会跳过一个脉冲。

如果单片机是EPROM,在编程其间,将用于输入编程脉冲。

·Pin29:当访问外部程序存储器时,此脚输出负脉冲选通信号,PC的16位地址数据将出现在P0和P2口上,外部程序存储器则把指令数据放到P0口上,由CPU读入并执行。

- 一种嵌入式时钟管理器的设计与实现(08-01)

- 基于ADC0809和51单片机的多路数据采集系统设计方案(10-29)

- 基于C8051F340驱动与采集的CCD光电遥测垂线仪(02-01)

- ARM仿真器与嵌入式系统设计讲解(02-12)

- 基于单片机C8051F060的智能功率柜的设计应用(01-12)

- 基于单片机的存储设备转储器(05-03)