双扫描使能低功率触发设计 限制SoC的移位模式中的功耗

所有的SoC使用扫描链来检测设计中是否存在任何制造缺陷。扫描链是专为测试而设计的,以串联方式按顺序连接芯片的时序单元。随着越来越多的功能被集成在SoC中,SoC中的触发器(时序单元)和组合逻辑的总数量不断增加。在扫描移位阶段,峰值功率是一个大问题,因为在完整的移进移出阶段,所有的触发器随着组合逻辑的切换而触发,而如果峰值功率超过允许的极限,移位数据可能会被破坏,这样由于伪故障而影响芯片的成品率。本文介绍了一个触发设计,可以对移位过程中的组合逻辑切换进行门控,从而保证设计的峰值功率和平均动态功率。

问题描述:设计中使用的测试扫描链连接设计的所有时序单元

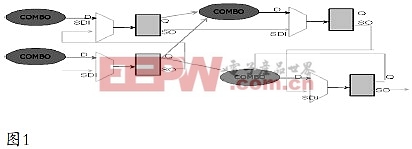

在多个链中,一个典型的触发器具有两个输出,功能输出(Q)和扫描输出(SO),在内部它们彼此短接在一起。触发器设计师提供了专门的扫描输出,可以在移位中轻松收敛保持定时。当SoC处于移位模式时,触发器的扫描输出直接连接到扫描链中下一个触发器的扫描输入,由于没有任何组合逻辑,这对保持定时来说是非常严峻的问题。因此,为了避免这个问题,设计师提供了专用的扫描输出,这是延迟版的功能输出(Q)。这样,在移进和移出阶段,功能输出Q与扫描输出SO一起继续根据扫描输入SI进行切换。由于功能输出Q切换,整个功能组合逻辑也在完整的移进移出阶段继续切换。图1显示了上述概念。

解决这个问题的动机

限制移位过程中的功率非常重要。挑战在于不影响设计的情况下,限制实例数和测试时间。目前,有几种方式来实现这一目标,如减少移频,建立多个移位域,然后按顺序运行它们,限制移位模式产生过程中的切换等。但所有这些解决方案会影响测试时间,从而增加测试成本。

因此,通过停止不必要的组合逻辑切换,可以显著减少移位过程中的峰值功耗。

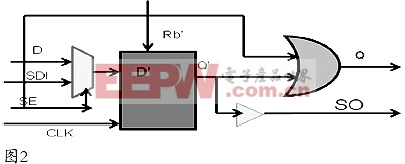

其中一种实现方式是对移位过程中的功能输出进行门控,然后在捕获周期中取消门控。之前在这方面已经有一些工作已经完成,而且已经有现成的技术(美国7650548 B2),通过扫描功能对功能输出进行门控。所以,思路很简单,因为在移位过程中扫描使能设置为1,功能输出将保持不变,在捕获周期时则取消门控,这样捕获到的就是最新扫描输入的值,而不是一些旧的或恒定值。见图2。

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)