数据处理指令之: SBC带进位的减法指令

6.7 SBC带进位的减法指令

1.指令的编码格式

SBC(Subtract with Carry)带进位的减操作指令,用于执行操作数大于32位时的减法操作。该指令从寄存器Rn>中减去shifter_operand>表示的数值,再减去寄存器CPSR中C条件标志位的反码(NOT(Carry flag))。并将结果保存到目标寄存器Rd>中,并根据指令的执行结果设置CPSR中相应的标志位。

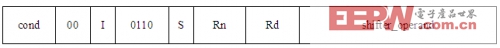

指令的编码格式如图6.8所示。

图6.8 SBC指令的编码格式

2.指令的语法格式

SBC{cond>}{S} Rn>,Rn>,shifter_operand>

① cond>

为指令编码中的条件域。它指示指令在什么条件下执行。当cond>忽略时,指令为无条件执行(cond=AL(Alway))。

② S>

S位(bit[20])决定指令的操作是否影响CPSR中条件标志位的值。当S=1时指令更新CPSR中条件标志位的值;当S=0时指令不更新CPSR中条件标志位的值。当S=1时,有下面两种情况。

· 如果Rd>不是R15,CPSR中的N和Z位根据指令的执行结果设置。C位根据指令操作是否产生一个进位(即一个无符号溢出)来设置;V位根据是否有带符号的溢出来设置。CPSR中的其他位不受影响。

· 如果Rd>是程序计数器R15,则当前程序状态的SPSR拷贝到CPSR。如果处理器处于用户模式或系统模式,则指令的执行结果不可预知。因为这两种模式没有自己的私有SPSR寄存器。

③ Rd>

指定目标寄存器。

④ Rn>

指定第一个源操作数寄存器。

⑤ shifter_operand>

使用ARM的通用寻址模式确定第二个源操作数。它影响指令编码格式中的I(bit[25])位和shifter_operand(bits[11∶0])位。

3.指令操作的伪代码

指令操作的伪代码如下面程序段所示。

If ConditionPassed{cond} then

Rd=Rn - shifter_operand-NOT(C Flag)

If S==1 and Rd==r15 then

CPSR=SPSR

Else if S==1 then

N flag=Rd[31]

Z flag=if Rd==0 then 1 else 0

C flag=NOT BorrowFrom{ Rn - shifter_operand-NOT(C Flag)}

V flag=OverflowFrom{ Rn - shifter_operand-NOT(C Flag)}

4.指令举例

SBC指令举例。

下面的程序使用SBC实现64位减法,(R1,R0)-(R3,R2),结果放到(R1,R0)

SUBS R0,R0,R2;

SBCS R1,R1,R3;

数据处理指令 SBC 带进位的减法 微处理器 ARM 相关文章:

- ARM指令寻址方式之: 数据处理指令的寻址方式(08-13)

- 数据处理指令之:AND逻辑与指令(08-13)

- 数据处理指令之:SUB减操作指令(08-13)

- 数据处理指令之: RSB减翻转指令(08-13)

- 数据处理指令之: ADD加操作指令(08-13)

- 数据处理指令之: TST测试指令(08-13)