采用非对称双核 MCU 提高系统性能

需要一系列状态标志位即可。此外,Cortex-M3 侧的 UART4 与 C28x 侧的 SCIA;以及 Cortex-M3 侧的 SSI3 与 C28x侧的 SPIA 在 Concerto 内部实现互联,不需要在芯片外部硬件连接,而是否使能这类功能则有 CortexM3 系统配置。

3.1 Message RAM 内存区

TMS320F28M35H52C 使用 Message RAM 实现 IPC 的数据通信。如图 5 所示,2K 字节的 MTOC Message RAM 用于从 Master (Cortex-M3)子系统向 Control(C28x)子系统传递消息;2K 字节的CTOM Message RAM 用于从 Control 子系统向 Master 子系统传递消息。由于两个子系统都配有 DMA外设,因此,DMA 也可以读写 Message RAM,从而提高系统效率。Message RAM 区通过 RAM 内存的读写权限保证了 Message 的互斥访问,例如,C28x CPU 与 DMA 可以读写访问 CTOM Message RAM 区,而 Cortex-M3 CPU 和 uDMA 只能读访问 CTOM Message RAM。同样,两个内核对于MTOC Message RAM 区的读写访问权限则正好相反。

Message RAM 仅仅作为 IPC 的数据缓存,IPC 还需借助于特定的控制逻辑电路来完成。如图 6 所示,Master 子系统和 Control 子系统都是通过 5 个寄存器来实现 IPC 的逻辑流程控制:IPCACK、IPCSTS、IPCFLG、IPCCLR、IPCSET。这 5 个寄存器都是 32 位,每一个 bit 对应于 IPC 的一个通道,因此最多可实现 32 个通道的握手通信。Bit0 到 Bit3 总共 4 个通道可以触发消息接收方的 IPC 中断,Bit4 到Bit31 共 28 个通道则需要消息接收方的软件查询来获取 Message RAM 中是否收到数据。如果两个内核之间仅仅传递状态和控制信息(例如 RTOS 中的 Semaphore),仅通过以上寄存器便可以实现,而无需 Message RAM 的参与。

以下通过举例 Master 子系统往 Control 子系统发送一帧数据,来简单介绍 IPC 模块的操作流程。

1. Cortex-M3 先在 MTOC Message RAM 中写入一帧数据;

2. Cortex-M3 置位 MTOCIPCSET(CM3 映射存储器区)的 Bit9,如图 6 所示,此时 MTOCIPCSTS(C28x 映射存储器区)的 Bit9 也将置位;

3. C28x 轮询 MTOCIPCSTS 的 Bit9,查询到 Bit9 已置位;(如果之前的操作是 Bit0 到 Bit3 其中之一, 则将触发 C28x 产生一个 IPC 中断)

4. C28x 读 MTOC Message RAM 中的数据,此时,Cortex-M3 成功将一帧数据发送至 C28x。

3.2 Shared RAM 内存区

大部分情况下,2K 字节的 IPC Message RAM 区能够满足 C28x 和 M3 子系统之间的数据通信,配合DMA,通信效率也可以进一步提高。如果用户希望一次性在两个子系统传递更大块的数据,另一种方法是通过 Shared RAM 内存。

TMS320F28M35H52C 有一个 64K 字节大小的 Shared RAM 区,总共 8 块 S0-S7,每块 8K 字节大小,如图 7 所示。Cortex-M3 可以设置让任何一块 Shared RAM 区由 C28x 或 M3 主控,比如,映射 S0 至C28x 侧以后,C28x CPU 和 DMA 可以读写 S0,而 M3 和 uDMA 将只能读 S0,不能写入和预取。

假如 Cortex-M3 需要一次性发送 6K 字节的数据到 C28x 侧,它可以先将 Shared RAM 区 S0 映射到本地存储器空间,接着通过 IPC 发送一个标志位给 C28x 来通知其可以将数据取走。

3.3 IPC 的软件驱动

controlSUITE 软件开发包中提供 2 种 IPC 的软件驱动库,IPC Driver 和 IPC_Lite Driver。IPC_Lite Driver 仅使用 IPC 寄存器来实现通信,不需要额外的 RAM,但是用户只能支持一个 IPC 中断服务 ISR,且不支持以队列形式来处理 IPC 请求。IPC_Lite Driver 使用方式如下:

1,主动发起数据请求的内核会首先调用 IPC_Lite Driver 提供的名函数。在这个例子汇总,M3 是发送数据的内核并执行“IPCLiteMtoCDataRead” 函数。

? IPC_FLAG2 是 C28 中断标志,指示 C28 内核一个消息到来。

? IPC_FLAG17 是响应标志,C28 用其指示 M3 核一个命令已经被处理。

? 需要读取数据的 C28 的地址也被作为一个参数传递给 C28 内核。

? 这个函数在 while 循环中被调用的原因是,它可能返回 STATUS_FAIL 并且不会发送信息给C28 直至 MtoC IPC 中断 2 和标志 17 可用, 之后,该函数返回 STATUS_PASS.

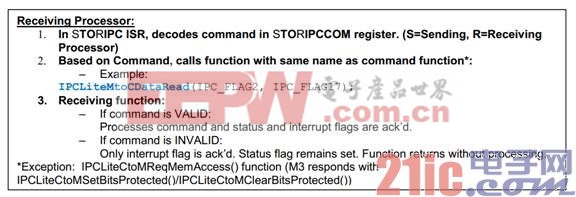

2,被动接收数据请求的内核会在 ISR 中解析其 IPCCOM寄存器的命令。这个例子中,C28 MtoCIPCINT2 ISR 知道标志置位,解析 MTOCIPCCOM寄存器的命令,识别出是读数据命令。

3,被动接收数据请求的内核会调用与主动发起数据请求的内核相同的函数名。这个例子中,C28 执行 IPCLiteMtoCDataRead, IPC_FLAG2 作为中断标志参数, IPC_FLAG17 作为状态标志参数。

4,如果接收到命令有效,IPC_Lite 的驱动函数会处理读命令并确认(acknowledges)状

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)